大家好、

我的板中有 AD582。 我想用 LF398-N 替换它。 请让我知道如何修改逻辑和逻辑基准信号连接。

采用 AD582的现有电路如下所示。

此致、

斯里坎特·卡丘

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Srikanth:

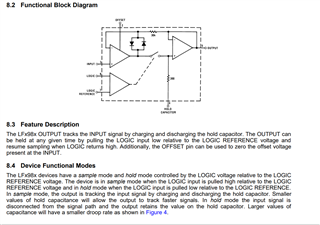

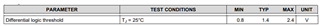

引脚7是逻辑基准引脚、引脚8是逻辑输入引脚。 当引脚8比引脚7高~2.4V 时将触发采样函数。 当引脚8比引脚7高~0.8V 时、将触发保持功能。

图18显示了如何配置器件、以在逻辑高电平触发采样。 图19显示了如何将器件配置为在逻辑低电平采样。

由于某种原因我无法查看现有原理图、可以再次尝试上传图像吗? 您只需将屏幕显示复制并粘贴到回复中即可。 或者、您可以将.pdf 文件直接拖到回复中。

您的逻辑高电压是多少? 您的逻辑低电压是多少? 是否要对逻辑高电平进行采样并保持逻辑低电平? 还是希望采样至逻辑低电平并保持逻辑高电平?

此致、

扎赫

尊敬的 Srikanth:

逻辑和逻辑基准之间的差异为0.8V 至2.4V 时将发生什么情况。 无论是在采样模式还是保持模式中、它将处于该范围之间的哪种模式。

0.8V 到2.4V 之间的范围不是器件的有效逻辑输入。 逻辑和逻辑基准之间的差异必须始终使器件处于逻辑高电平或逻辑低电平状态。 如果器件未处于有效的逻辑高电平或逻辑低电平状态、我们无法预测器件是处于采样模式还是保持模式。

阈值= 1.4V 的意义何在?

1.4V 是 典型 逻辑阈值。 确切的阈值电压会因单个器件而异、因此还必须考虑最小和最大阈值电压。 逻辑高电平输入必须始终大于最大阈值(2.4V)、而逻辑低电平输入必须始终小于最小阈值(0.8V)。

下面突出显示的句子不清楚。 您能否重新表述?

当差分逻辑电压(引脚8 -引脚7)小于0.8V 时、将触发保持功能。

请注意、这些是器件识别有效逻辑信号所需的最小和最大阈值电压。 考虑在0V 时引脚7 (逻辑基准)连接到数字接地的情况。 器件引脚8的典型逻辑输入对于逻辑低电平为0V、对于逻辑高电平为5V (或3.3V)。

在本例中、0V 为有效逻辑低电平输入(0V < 0.8V)、5V 为有效逻辑高电平输入(5V > 2.4V)。

3.3V 也是有效逻辑高电平输入(3.3V > 2.4V)。

此致、

扎赫

您好、Zack、

我们将用 LF398-n 替换 AD582KD。 在基准级测试中验证 AD582KD 时。

下面附上了测试情形和观察结果、

已提供输入: +Vs = 15V、-Vs =-15V、+Logic =+15V。

结果:

|

数据表中提及的详细信息 |

计算值/实际值 |

测量值 |

|

保持模式 |

> 13V |

> 11.6 V |

|

采样模式 |

< 14.2V |

小于11.6V |

上方附加的原理图。 请确认与有差异的原因、请参阅数据表。

*低成本采样保持放大器数据表(修订版 A)(analogue.com)

此致、

Pradeepraj M