主题中讨论的其他器件:TLV1701, TINA-TI

您好!

使用为 TLV1704-SEP 提供的默认 TINA-TI 模型(即 TLV1701 SPICE 模型)时、我注意到以下行为。

如下图所示,当使用默认的型号 TLV1701时( SPICE 模型日期: 2013年12月16日),我们可以看到输出(COMP_OUT)在供应斜升期间保持低水平。

然而、当使用 2023年08月30日 提供的最新 SPICE 模型时、我们可以看到输出变为高电平、然后在电源电压上升期间变为低电平。

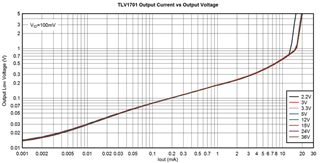

通过下图(红色 COMP_OUT)、我们可以看到、当 VCC 约为2.17V 时、比较器将输出驱动为低电平。

我还使用另一个 Spice 仿真器运行该仿真并获得相同的结果。

我的假设是、较新的 Spice 模型反映比较器的预期行为、这意味着比较器在 VCC 达到2V 之前无法驱动输出。

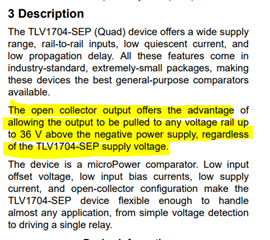

1. 在功率上升期间、当 VCC < VCC min (2.2V)时的预期输出状态是什么。

2.由于输出端的外部上拉电阻,输出应该跟随 VCC 还是应该是低电平?

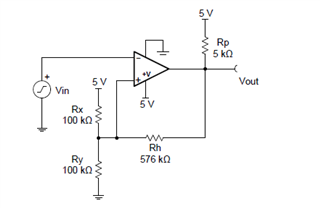

我正在使用的电路与下面的电路相同、只是 VCC = 3.3V、并且我使用了不同的电阻器值来获得不同的阈值。