Other Parts Discussed in Thread: INA280, INA281, INA186, INA2191, INA4290

主题中讨论的其他器件:INA186、 INA2191、 INA4290、INA280 、INA281

您好、TI 专家!

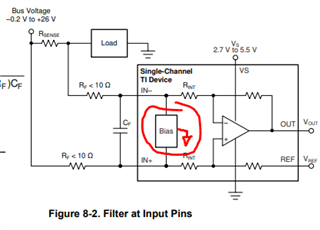

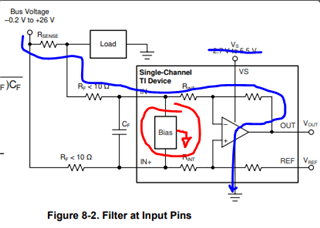

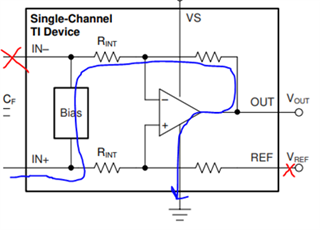

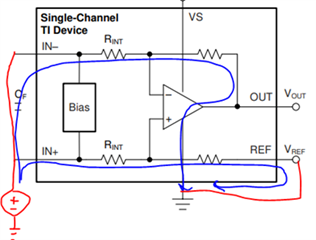

我使用的是 INA4181A2IPWR、发现它在关断后具有很大的功耗。 测试如下。 IN+1和 IN-1通过 RSENSE 直接连接到电源 B+。 该器件没有 MOS 管控制、始终为 INA4181A2IPWR 输入引脚 IN+1供电。 和 IN-1。 在测试系统关断电源时、我们发现 IN+1引脚将导致75uA 的电流、这对于我的产品设计而言是不可接受的。

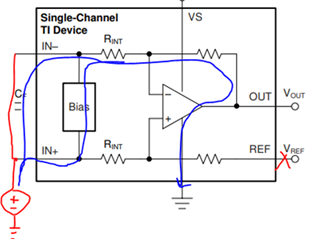

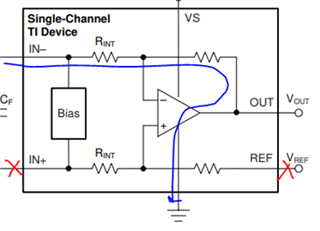

如所附的规格图中所示、我将 REF 接地并将其断开、但75uA 电流没有降低。

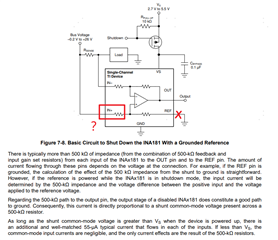

因此、我想知道此 INA4181A2IPWR 的 IN+1引脚的内部方框图是否等于将250KΩ Ω 电阻器接地? 此 IN+1引脚如何在内部连接? 我想介绍如何降低功耗、或者您有没有更好的解决方案?