请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM2903-Q1 您好!

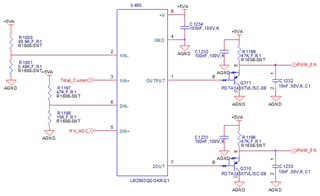

我的客户要求进行原理图审核。

Output1:4.5V 高

Output2:1.2V 高

目的是输出最终 PWM_EN 级的低电平输出。

请查看原理图。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Cho:

目前、1IN-电压为0.496V、2IN-电压为1.210V。 这意味着只要 Total_Current < 0.496V、输出将拉至低电平;只要 Total_Current > 0.496V、输出将拉至高电平。 当 HV_ADC 小于1.210V 时、2OUT 将拉至低电平;当 HV_ADC 大于1.210V 时、2OUT 将拉至高电平。

LM2903-Q1的输入共模电压要求是 V-到 VCC -在整个温度范围内为2V;这意味着您需要将输入电压保持在该范围内以确保比较器正常运行。 IN-都在该范围内、但您需要确保 Total_Current 和 HV_ADC 也在该范围内。

预偏置 PNP 对我来说似乎很冗余;您选择在设计中使用它们的具体原因是什么? 如果比较器的输出拉低、它将导通将 PWM_EN 拉低的 PNP。 PNP 不会执行反相操作、因此在我看来、您可以通过将比较器输出连接在一起并添加一个奇异上拉电阻器来减少元件。