Other Parts Discussed in Thread: OPA838, OPA838DBVEVM

主题中讨论的其他器件:OPA838、

尊敬的所有人:

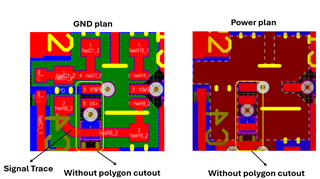

我想使用德州仪器的参考设计作为 OPA838的布局的参考、我注意到这个参考设计是一个4层的板:

正如我们在图片中看到的、 GND 和电源平面图都有多边形切口、但我注意到、引脚5、6、2没有多边形切口、其中的引脚是正极和负极、使能引脚、为什么我们把 GND 和电源平面图保留在这些引脚的下方?

我的第二个问题是:

在此布局中、我可以在信号布线下方看到(图中的信号布线)、我们在布线下方具有不连续的 GND、这是否会从布局角度导致任何问题? 考虑到高速布线的属则规则、我们应该为信号布线提供一个返回路径、该返回路径是 信号下方的 GND 规划、但在本例中、我们没有它或我们有它、但以一种不连续的方式提供。 请告诉我是否正确、如果正确、我们如何优化布局?

此致、