Other Parts Discussed in Thread: THS4561, ADS8881, THS4551, THS4531A, LMH6554

主题中讨论的其他器件:ADS8881、、 THS4531A、THS4561 、 LMH6554

您好、TI 专家。

我最终完成了 DAQ EVB 电路板设计、 但测试结果并不理想 、请帮助分析此处的问题。

我要附上我的 TINA 仿真文件、我的 EVB 板原理图以及我的测量结果。

下面是我们刚刚介绍的 EVB 原理图、

e2e.ti.com/.../7966_2B00_ADS8881-DAQ-Reference.pdf

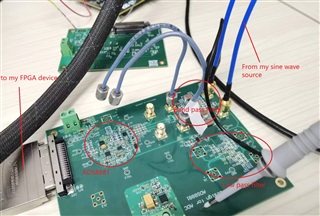

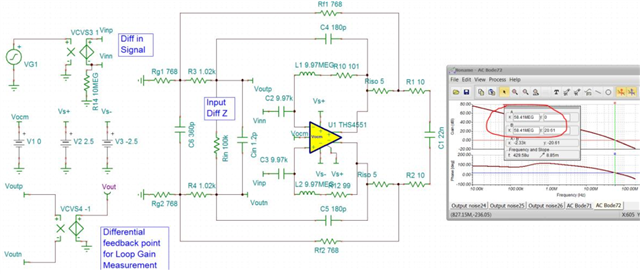

我的 DAQ EVB 使用 TI 的 ADS8881 ADC、并且在 ADC 前端有一个带通滤波器(中心频率1KHz)和一个低通滤波器(截止频率20kHz)。 这两个滤波器都使用 THS4551。 我使用 SMA 电缆连接正弦波源/滤波器/ADC。

如果没有任何滤波器、ADC 按预期工作、我可以从 ADC 结果中获得 SNR ~82dB。 这个结果是可以的、它告诉我 ADC 和我的 FPGA 器件工作正常。 ADC 的采样速率大约为1MSPS。

但当我添加带通滤波器或低通滤波器时、SNR 会下降到大约50dB。

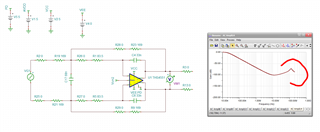

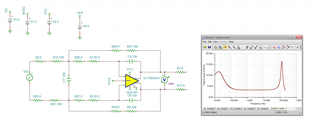

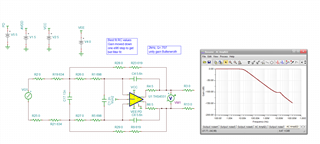

我用 TINA 仿真带通滤波器和低通滤波器、都不错、在 PCB 板上这样做时、滤波器根本没有提高性能。

实际上、在我对 PCB 进行布局之前、我已经要求 TI 提供有关设计/仿真的帮助。 请查看下面的链接。

适用于高精度 ADC 的低噪声、低失真带通滤波器

下图是不使用任何滤波器的 ADS8881结果、结果正常

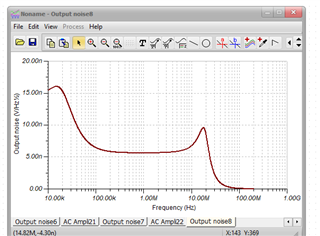

下图是在输出端添加带通滤波器

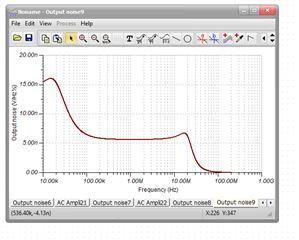

下图是添加低通滤波器

下面是我的带通和低通滤波器仿真文件

e2e.ti.com/.../DAQ-1kHz-BPF-EVB.TSC

e2e.ti.com/.../DAQ-1kHz-LPF-EVB.TSC