工具与软件:

您好!

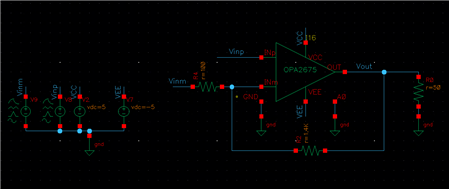

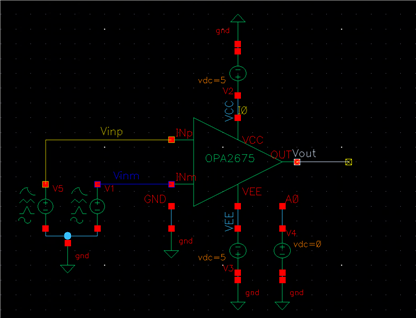

我将 在 Cadence 虚拟测试台对 OPA2675使用未加密的 PSpice 模型。 我正尝试 用各自的运算放大器来驱动两个 FET 的栅极、我喜欢 OPA2675 、因为它具有较快的转换速率和高输出电流。 在仿真过程中、我注意到 OPA2675的压摆率低于我的预期。 下面是我用来确定 OPA2675特征的一个单独测试台的屏幕截图:

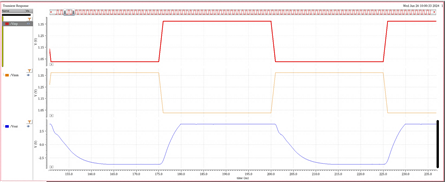

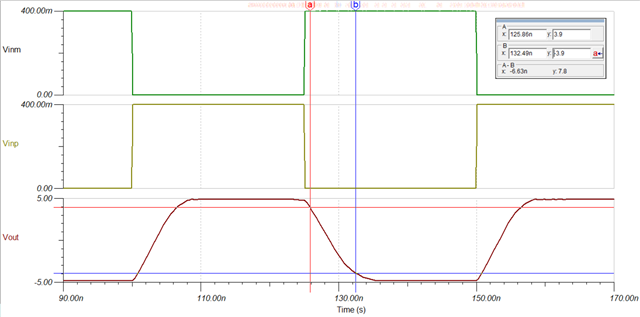

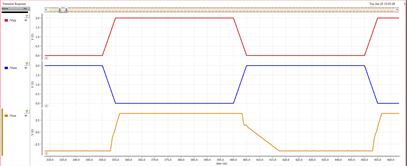

我将理想的差分信号应用于输入端子、而电源轨偏置为 ±5V。 下面是该测试台的瞬态仿真结果的屏幕截图:

运算放大器输出的上升沿似乎与数据表一致、但下降沿降级。 有人能解释一下为什么我会得到这样的结果吗?

感谢您的帮助!

Braden