工具与软件:

大家好!

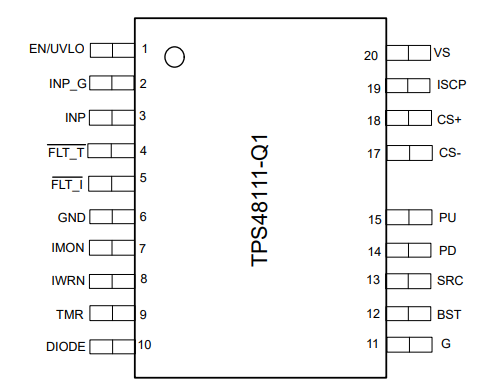

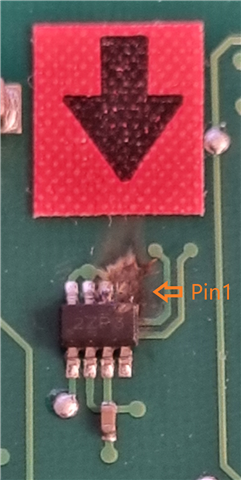

我使用的是 INA241A3-Q1分流放大器。 我有一些问题。 我们拥有组装所需的板。 在测试过程中、一个 INA241A3-Q1已烧毁:

我想了解这可能是什么原因造成的。

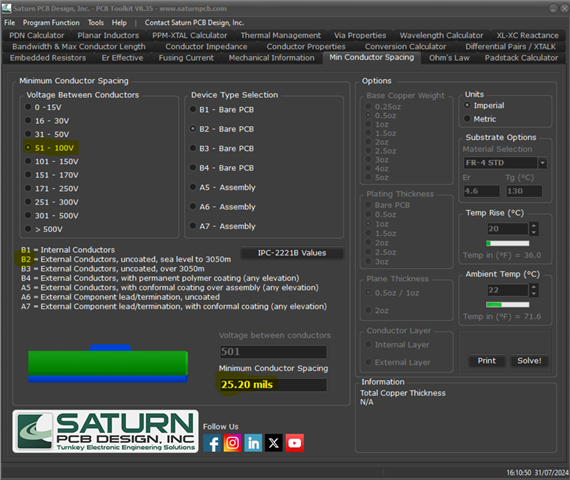

我已经确认外部层(待采用土星印刷电路板)上的最小间隙应约为25mil:

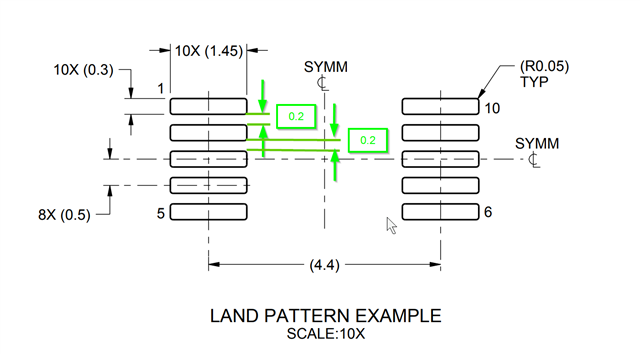

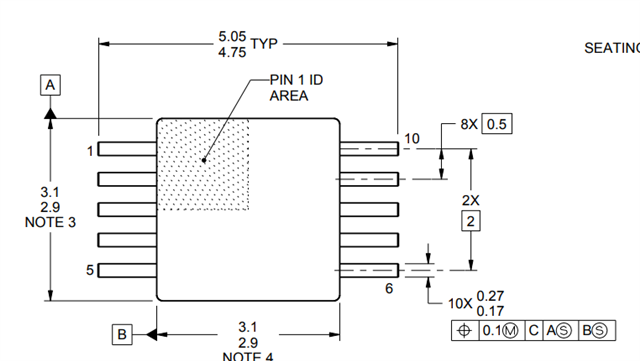

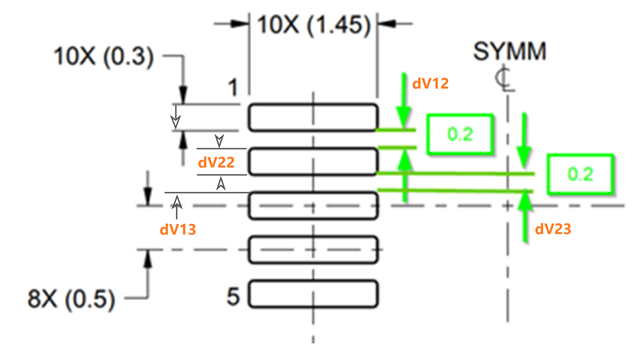

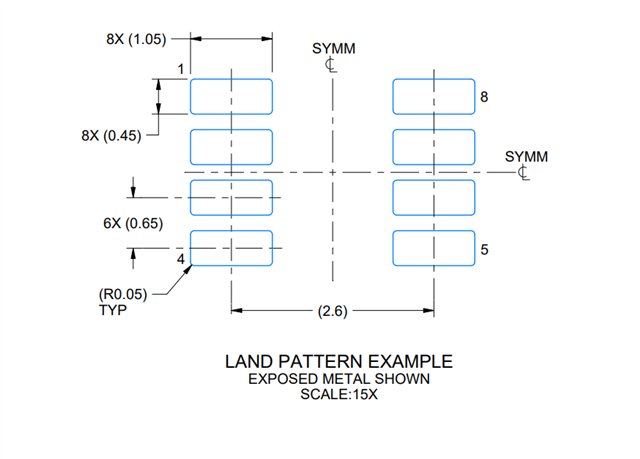

但是、根据数据表、相邻引脚之间的建议间隙为0.2mm (8mil):

该元件能够承受高达120V 的共模电压!

由于引脚1是"+"端子、而引脚2是 GND、因此根据间隙/爬电距离计算、似乎是个问题。

我正试图调查这个问题,并且像如果有人有一个想法。

此致、

Alex