主题中讨论的其他器件: OPA392、 INA592、OPA2392、OPA388

工具与软件:

尊敬的所有人:

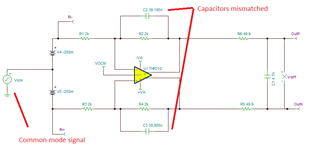

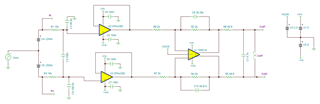

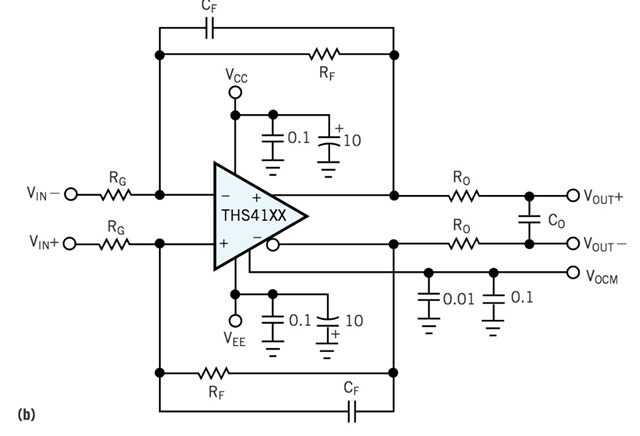

我正在设计一个全差动一阶低通滤波器、作为 ADC 驱动信号链的一部分。 我要使用 THP210、并将低通3dB 切口设为~2khz。

设计如下(感谢 EDN 提供的草图!)

我得到 VCC = 5V、VEE = 0、VCM = 2.5V。

RG= 384=2k (使用 Vishay Dale 4电阻阵列、匹配比为0.01%)

CF=39nF NP0 1%容差。

R0= 49.9和 C0=4.7n。

R0是 ADC 差分之后。

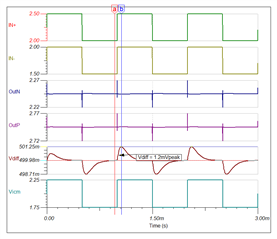

最后、我的输入信号是两个输入引脚上的偏移方波(同相)、方波频率为1kHz。

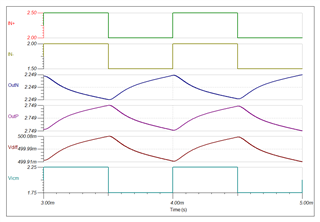

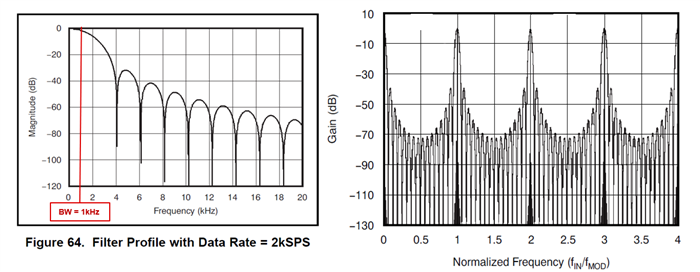

即对于500us、我将得到 VIN+=2V 和 VIN-=1.5V、对于500us、我将得到 VIN+=2.5V 和 VIN-=2V、然后重复。 显然、我希望我的输出信号是两个信号之间的差值(即、在本例中 、一个输出应处于 VCM+0.5/2=2.75、另一个应处于 VCM-0.5/2=2.25V。 我的电路的总体用途是测量这个差值的变化(非常缓慢、<10Hz)。 我将在 ADC 上以大约20Hz 的频率运行 SINC 滤波器(即、不要在这模拟输入部分进行更积极的低通滤波、因为我的印象是它需要大电阻器值、从而会给我的信号增加明显的噪声...)。

现在转到我的问题; 我认为我在 Cf 的计算中做了正确的事情来提供2khz 低通滤波器 、但增加这个电容器是否会使设计中的 CMRR 变得一团糟-在这种情况下会导致我的输出中出现1kHz 瞬变? 如果可以、我的印象是这不一定重要、因为差动 ADC 通常会提供>> 100db CMRR -或者这是数据表中的"真实情况"吗、在实践中、由于这种额外的噪声注入、我的电路将受到影响?

我认识到这 可能是 一个琐碎的问题,但在任何地方都找不到一个特别好的解释在网上...

非常感谢您的建议。