Other Parts Discussed in Thread: LMH7322

工具与软件:

您好、感谢您阅读这篇文章!

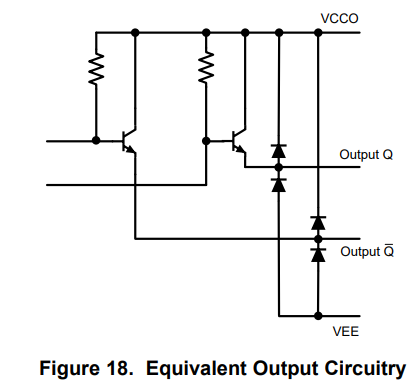

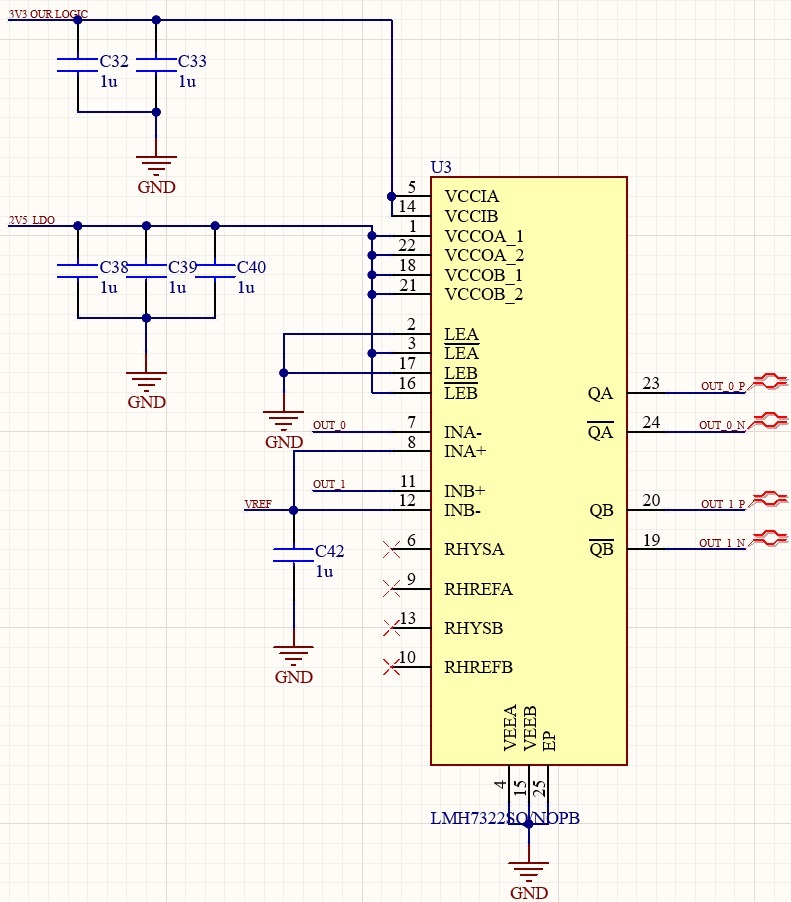

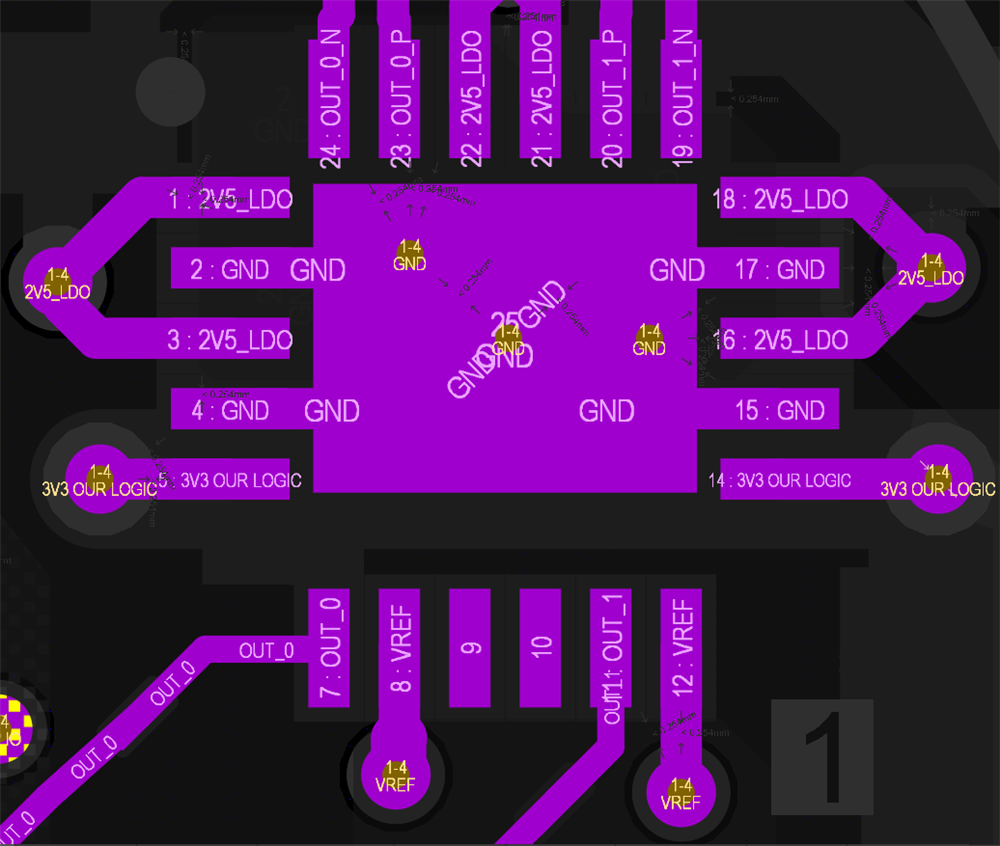

我有一个 PCB、其中一个定制芯片产生四个 LVCMOS 1.2V 输出-名为 OUT_0、OUT_1、OUT_2、OUT_3 -我必须将其转换为 LVDS。 我考虑采用两个具有0.6V 基准电压的 LMH7322SQ/NOPB 比较器来实现此目的。 但是、输出卡在1V 以上。 我的实现方式如下(两个比较器相同):

所有电压均设置正确。

我知道引脚 6和13缺失。 这就是我的 想法、因为我不希望有任何迟滞、所以我让它们保持未连接状态(并试图让信号进入芯片下方、但最后没有执行)。 我 想问题不是将任何电阻连接到引脚2和3 (我不需要任何锁存功能)、但我不确定。

感谢您的观看!

先生