主题中讨论的其他器件: TLV8542

工具与软件:

你好

我们计划在设计中使用 TLV8542或 OPA2391、以连接高阻抗累加器(>100兆欧姆阻抗累加器)

当我们的器件处于存储模式时、放大器不通电、

我们将用作具有单位增益的同相放大器、以将信号缓冲到我们的系统中、累加器(+/-0、3VDC)直接连接到放大器的 IN+、

请能否分享有关 TLV8542和 OPA2391在器件未通电时保持偏置电流性能的数据

期待您的支持

此致

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你好

我们计划在设计中使用 TLV8542或 OPA2391、以连接高阻抗累加器(>100兆欧姆阻抗累加器)

当我们的器件处于存储模式时、放大器不通电、

我们将用作具有单位增益的同相放大器、以将信号缓冲到我们的系统中、累加器(+/-0、3VDC)直接连接到放大器的 IN+、

请能否分享有关 TLV8542和 OPA2391在器件未通电时保持偏置电流性能的数据

期待您的支持

此致

TLV8542和 OPA2391的输入均具有钳位二极管至 V+。 如果输入电压比 V+高0.3V 或0.5V 以上、则有电流流过二极管、如果电流达到10 mA、则可能会损坏器件。 (此外、流入 V+的电流可以(部分)为连接到 V+的任何器件加电。) 为避免这种情况、请使用开关来断开运算放大器输入、或使用具有关断引脚的运算放大器、并保持通电。

但是、如果 输入电压比 V+高小于0.3V、则 将不会有明显的电流流动。

齐亚德, 我同意克莱门斯。 CMOS 放大器的"偏置电流"是输入 ESD 结构的漏电流。 当放大器未通电并施加低于0.3V 的输入信号时、会在二极管上产生较小的正向偏置。 但是、在输入大于0.3V 之前、二极管完全导通的二极管曲线拐点将不会发生。 然而、在 Vin < 0.3V 并且放大器未通电的情况下、偏置电流不再定义、可能大于指定的偏置电流。 但是、 在这种情况下我不会期望高电流。

此致、艺术

感谢 Clemens & Art

我对 TLV8542/OPA2391关闭(未上电)时的输出阻抗有相同的问题

在本例中、其中一个放大器缓冲高阻抗电极、另一个放大器的输出为高阻抗参考电极供电(通过同相单位增益放大器-缓冲器)、

当系统处于存储模式时,系统中没有电池,所以放大器关闭, 如果我们的基准电极有一个电位在-0,3和+ 0.3V,是否有任何可能反向收缩电流冲放大器输出,我们的基准电感可以仿真为一个 µAH μ F 容量的电池?

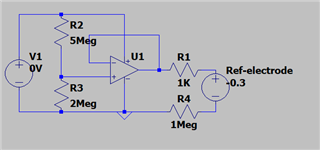

这是设计

在其他情况下、我们可以知道在器件 U1未通电时电流会超出 R1的阈值吗? 我们需要避免使参比电极放电

提前感谢您的支持

此致

Zaid

当放大器未通电时、输出阻抗将不为零。 大多数情况下、我们不指定器件处于关断状态时的输出阻抗。 要获得具有高输出阻抗的放大器、您可能需要使用具有禁用功能的放大器、该功能设计为在禁用时具有高输出阻抗。 请注意、并非所有具有禁用功能的放大器都具有高输出阻抗。 OPA334 是专门针对该功能而设计的。 下面是一篇讨论此主题的 E2E 文章: 关于 OPA334输出泄漏的 E2E . 在这种情况下、您可能会发现当前设计的泄漏电流是可以接受的 、因为您的信号电平非常低、因为此电压电平足够低、可避免过多导通任何二极管。

此致、艺术

Zaid

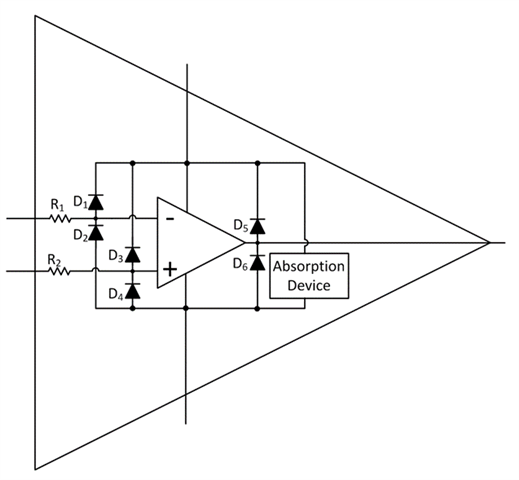

我不能给你太多的细节,因为这是专有的。 我可以说、它将具有如下所示的 ESD 保护结构。 此外、它是一种轨到轨 CMOS 输入/输出、因此本文档展示了基本的输入和输出结构、并说明了它的工作原理: 运算放大器输入和输出摆幅限制

此致、

艺术