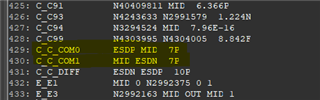

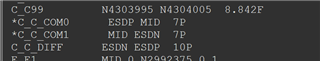

工具与软件:

您好!

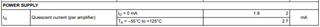

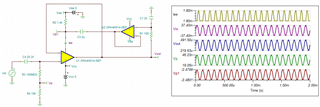

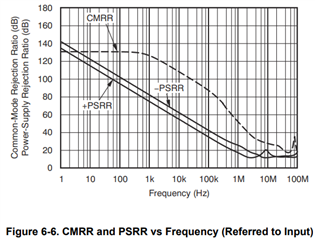

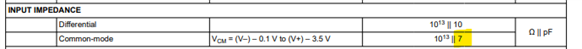

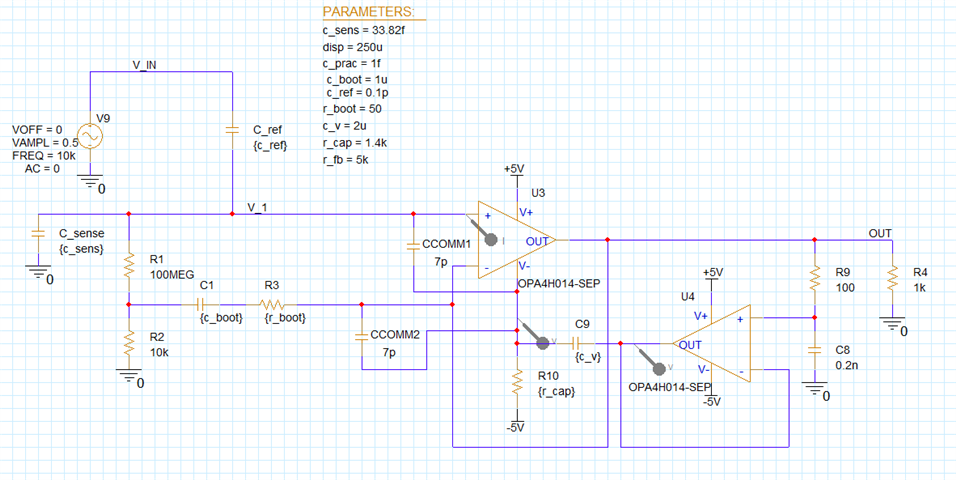

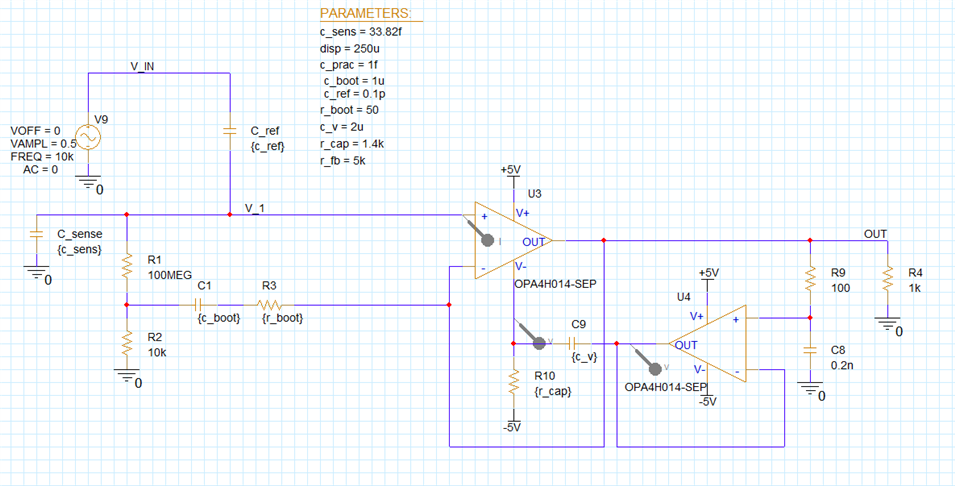

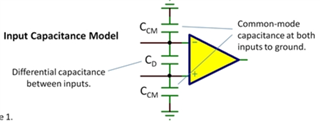

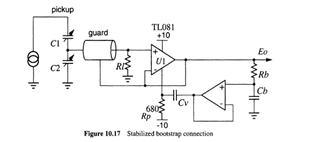

我尝试在航天应用中的小型电容传感器(0.033-0.1pF)上使用前端放大器。 我喜欢 OPA4H014-SEP、因为它具有较低的偏置电流、电流和电压噪声密度以及相对较低的共模输入电容。 为了提高测量相对于传感器的灵敏度、我希望使用自举连接方式连接运算放大器的负极端子、如下所示(使用 Rb、Cb、未命名运算放大器栅极 CV 和 Rp):

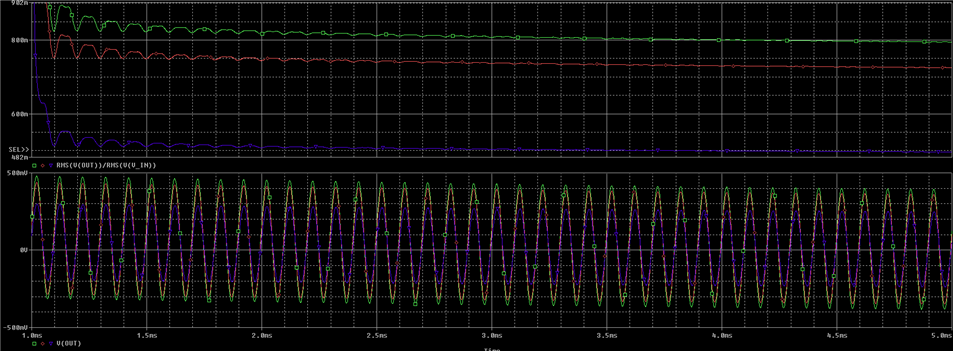

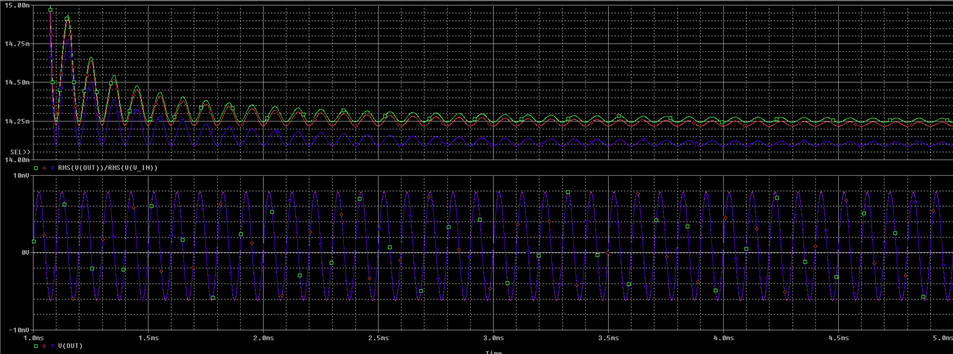

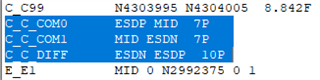

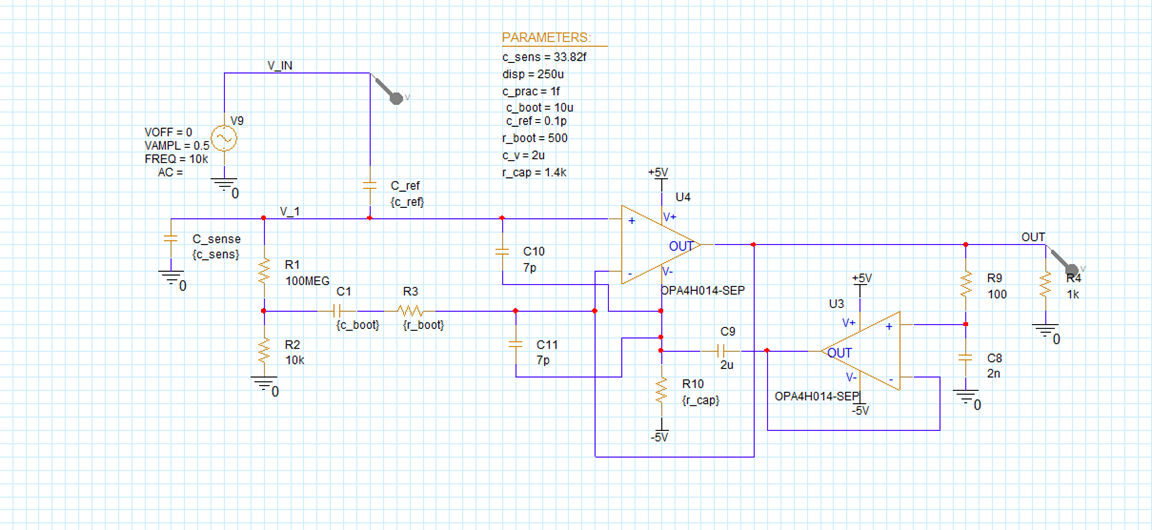

根据我要读的内容、如果共模输入电容被连接至负电源、这应该有效地减少共模输入电容的影响。 我之前在查看此器件的 PSPICE 模型、但当时很难确定这是否是此器件的情况。 当我使用这种拓扑运行仿真时、我没有打算的效果。 如果我注释掉两个输入端的共模电容、并在我的仿真中添加具有相同值的分立式电容器(电容器的一端在输入端、另一端在负电源引脚)、我确实可以实现预期的效果。 我当前的仿真设置图片如下所示:

我想知道这是否为仿真起见进行了有效的更改、或者您是否有任何替代建议来引导共模电容的影响。 或者、如果您知道器件的噪声密度和输入偏置电流相似但共模电容较小、那就很好了。 输入信号是10kHz、因此带宽仅需要足够支持这一点。 谢谢!