Other Parts Discussed in Thread: JFE150, OPA197, REF3212, JFE2140, JFE2140EVM, OPA1637, OPA1692, OPA202, OPA145, REF3425, LM134, TINA-TI

https://e2e.ti.com/support/amplifiers-group/amplifiers/f/amplifiers-forum/1427239/jfe2140-opa892

器件型号:JFE2140主题中讨论的其他器件:、 OPA1637、JFE150 、OPA197、 OPA1692、OPA202、 OPA145、 REF3425、REF3212 、 LM134、 TINA-TI

工具与软件:

您好、TI:

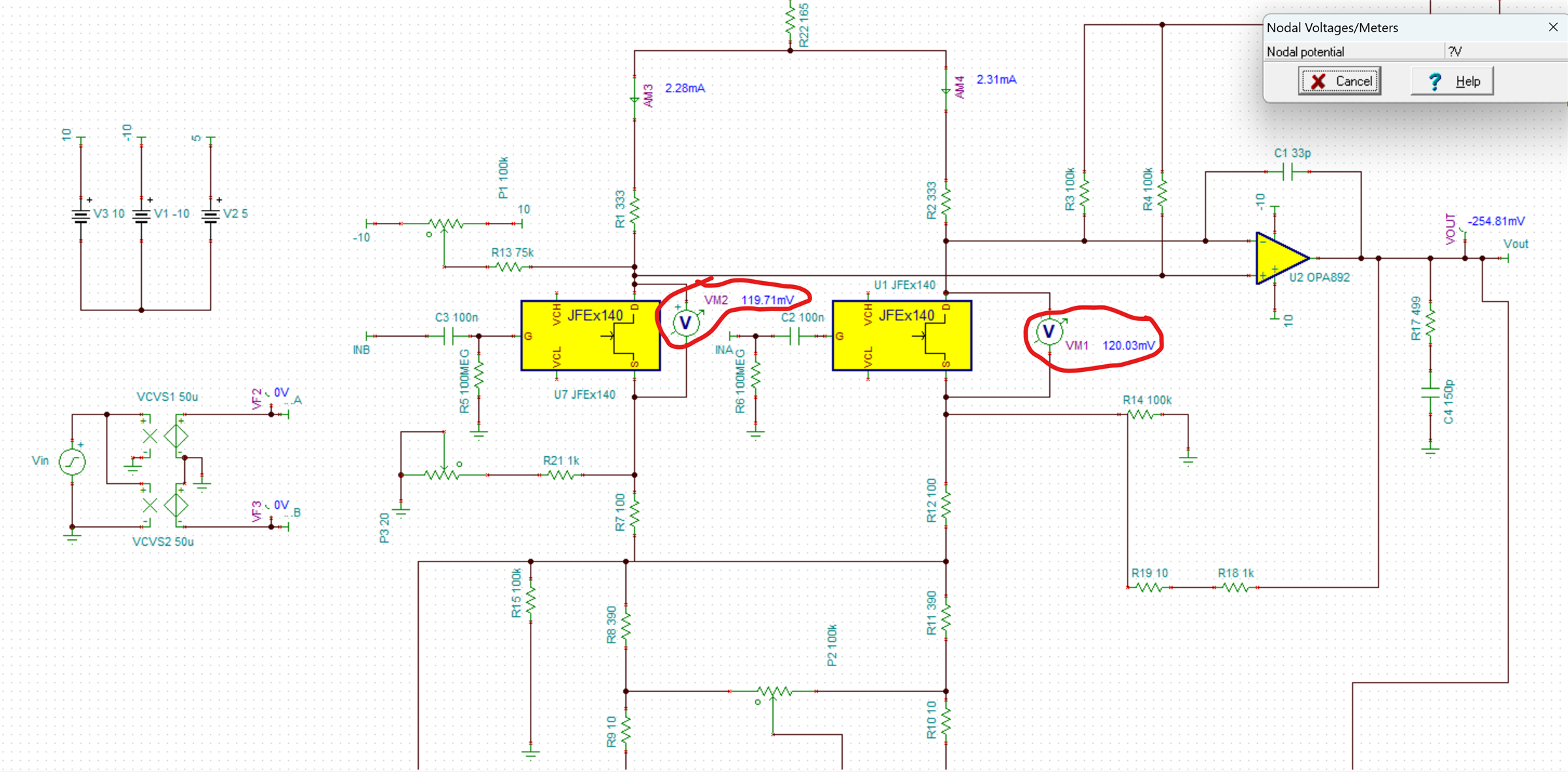

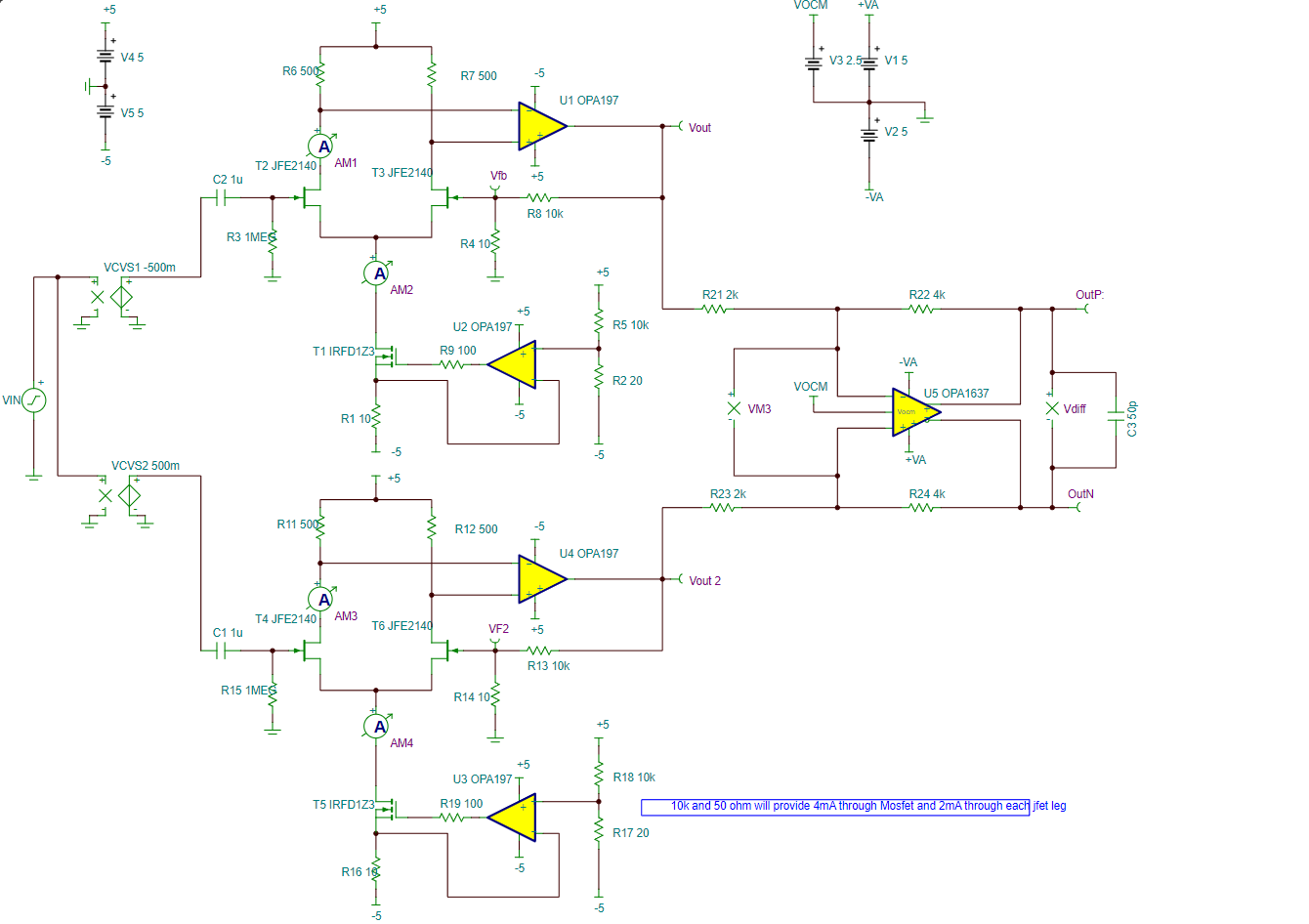

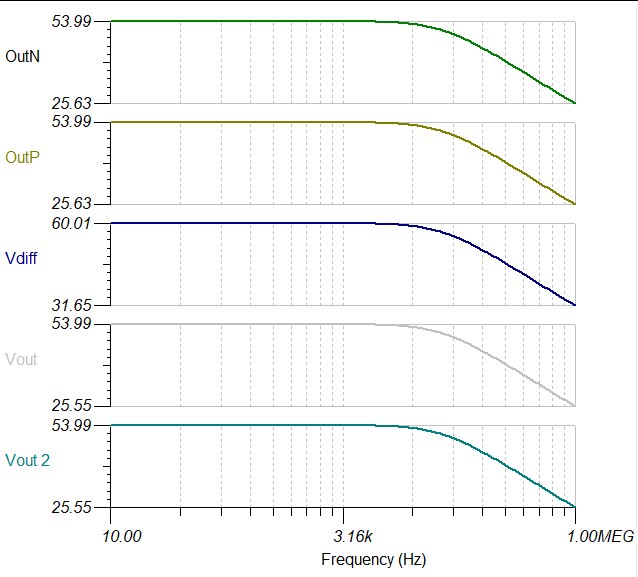

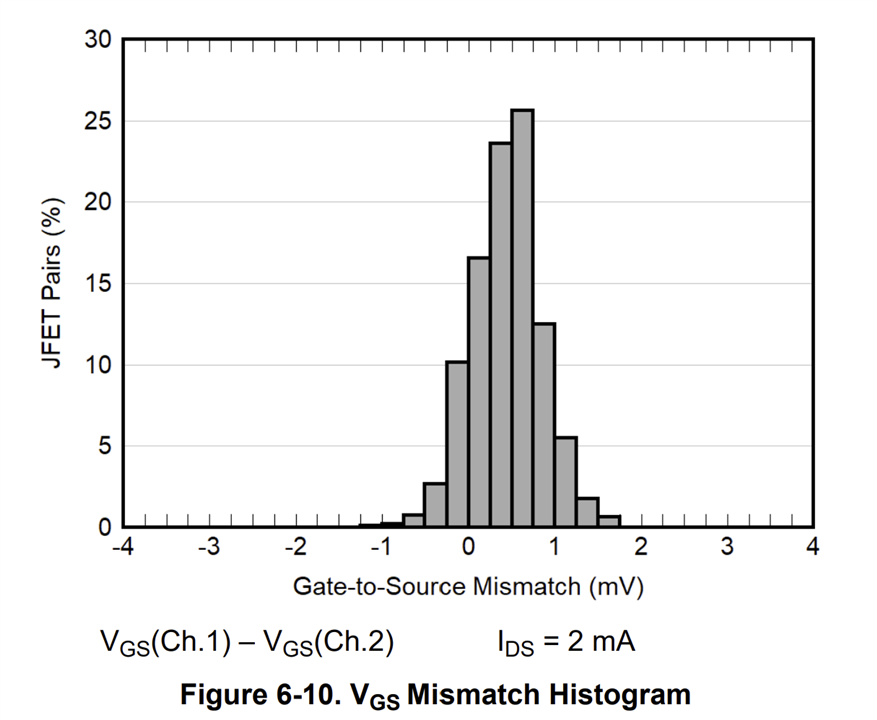

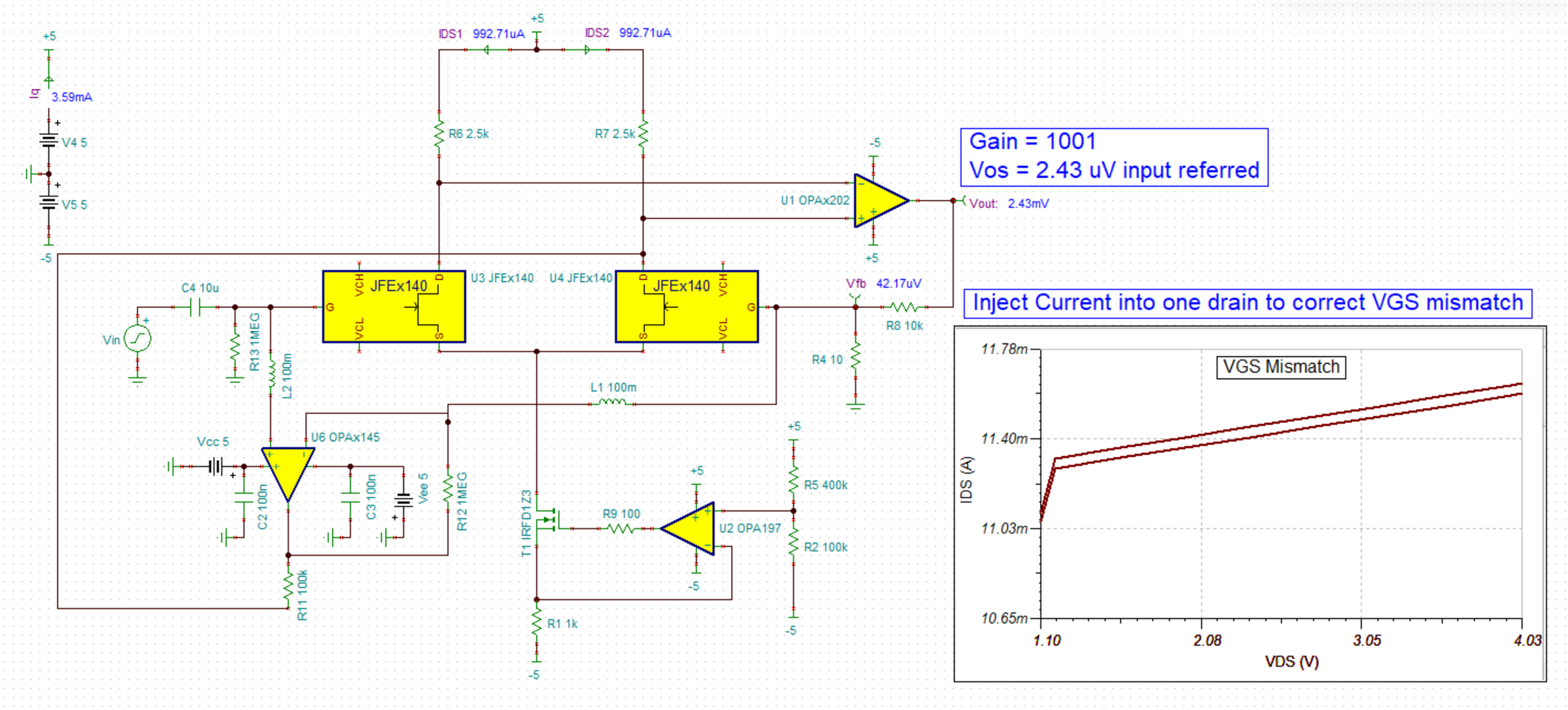

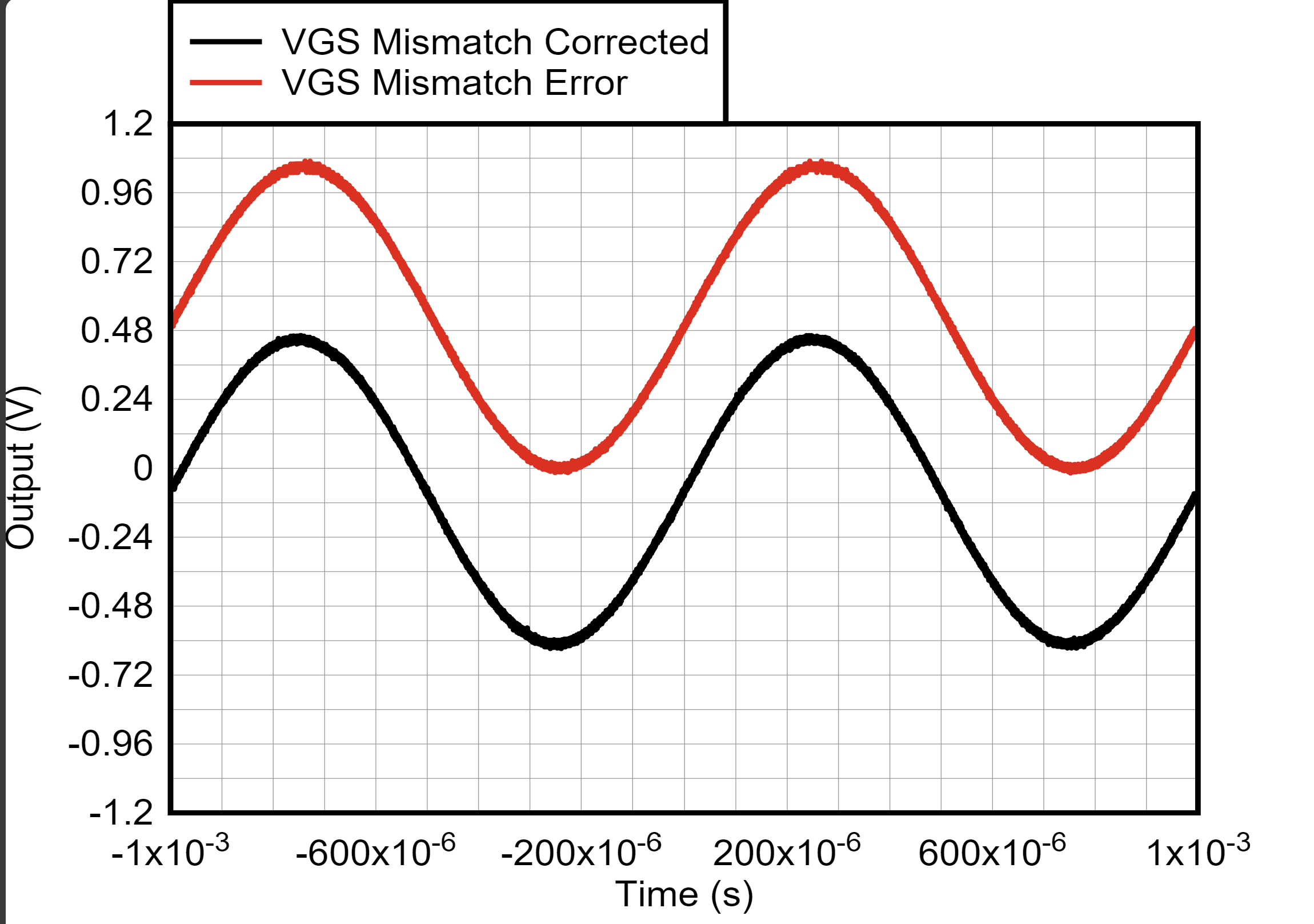

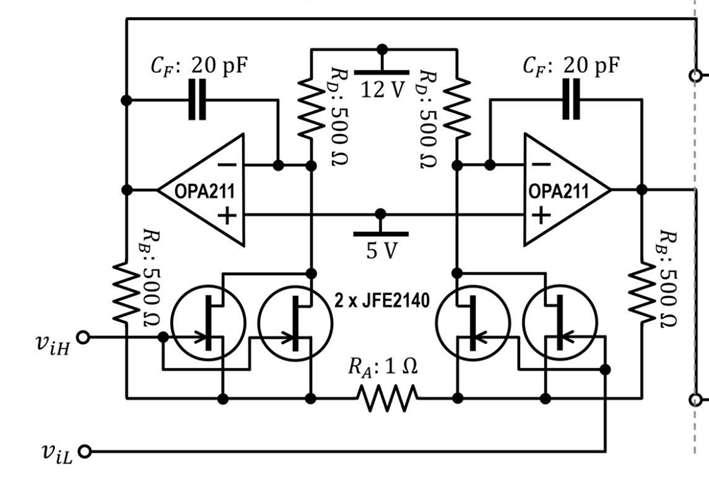

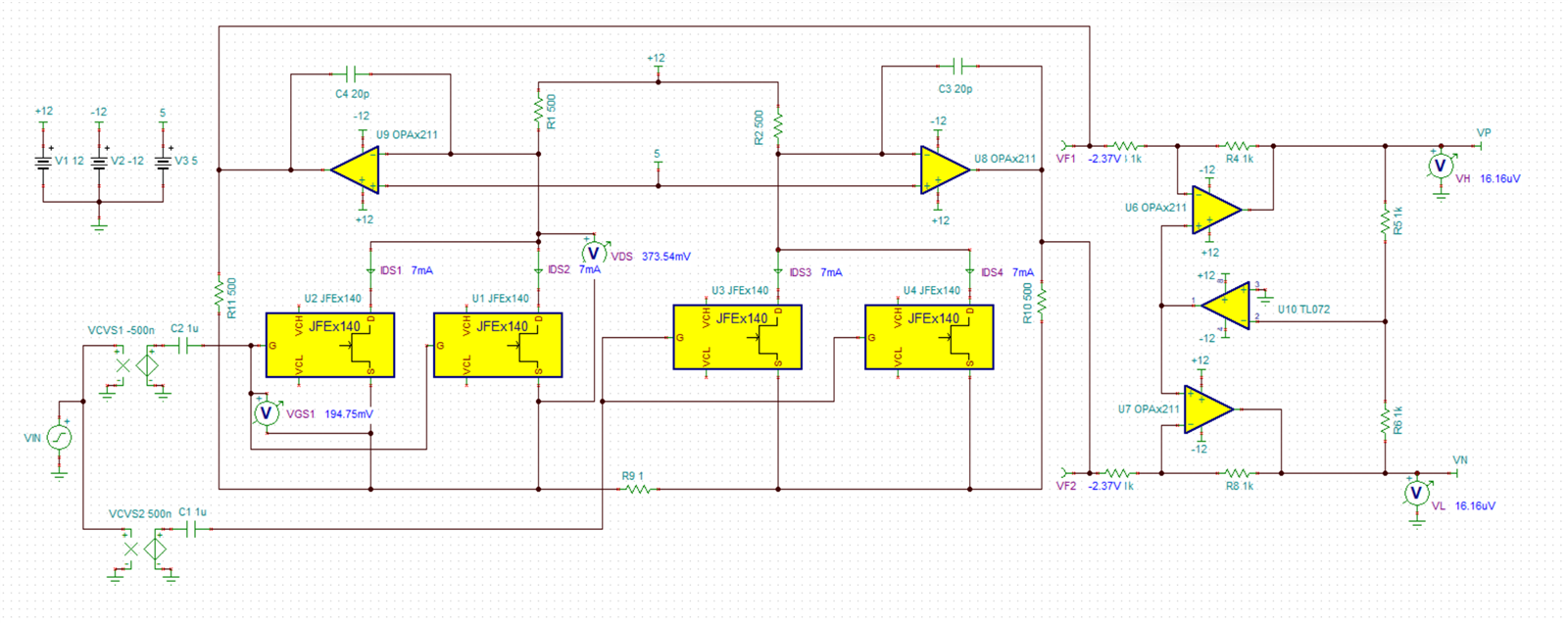

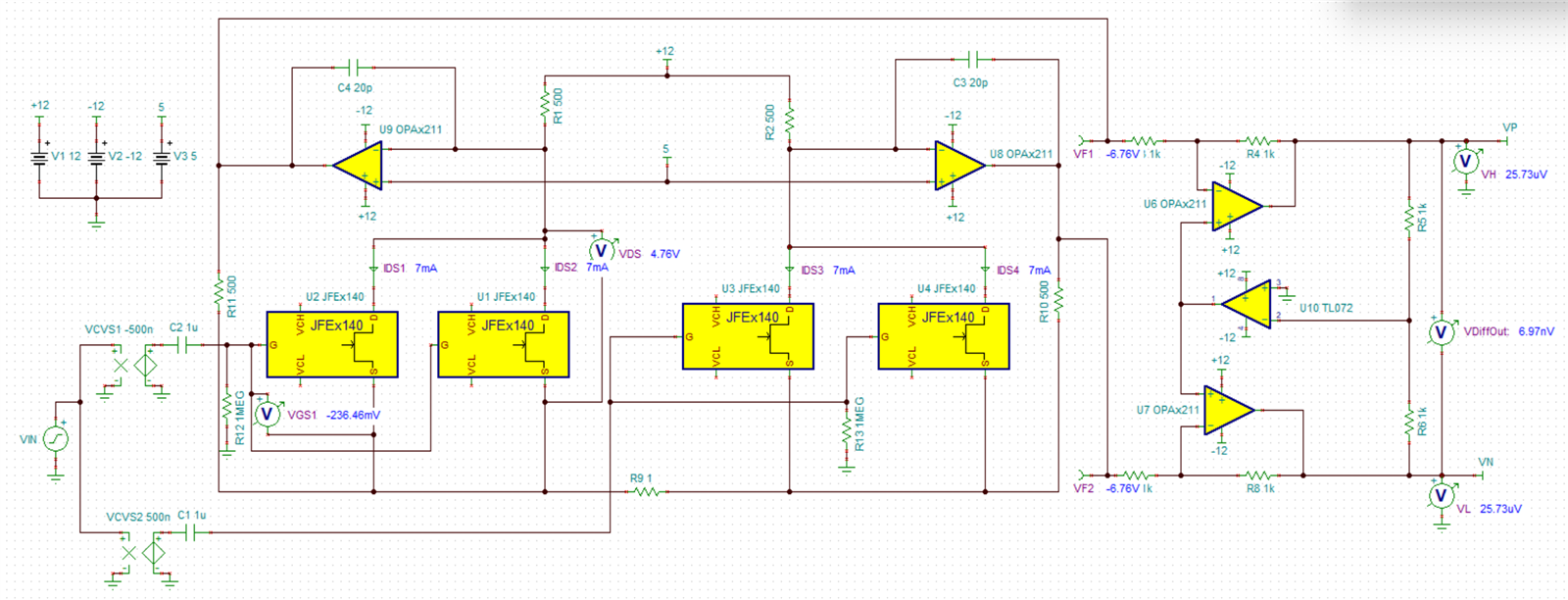

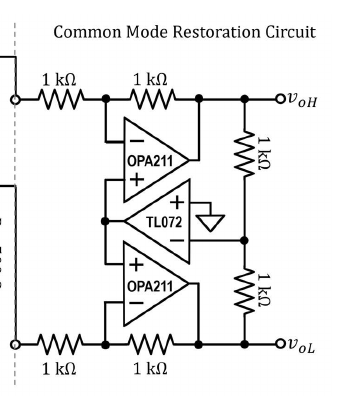

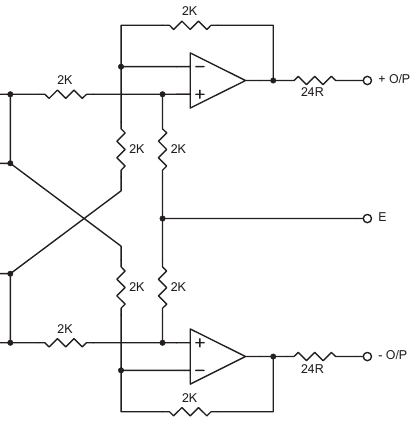

我要仿真一个电容为66nF、100K 的压电换能器、并连接到该前端放大器以实现极低的噪声性能。 仿真结果严重错误。 任何人都可以告诉我、我的仿真中有什么问题。 此外、我想计算这个电路在10Hz 至20KHz 的 CMRR。 请告诉我。 我打算使用增益为10的放大器。

e2e.ti.com/.../JFET_5F00_Frontendv2.TSC

问题出在哪呢?