Other Parts Discussed in Thread: BUF802

工具与软件:

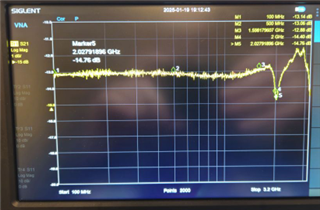

大家好、我正在使用 BUF802测试我的设计、但我的设计在2GHz 频率下"深度"。

我做了一些实验、移除了直流阻断电容器、不再看到深部。 (我做了几处修改、移除了 LF 和中频路径、深频率或振幅没有变化)

可能与电容器的封装/电感/ESR 有关? 您是否有推荐 PN? 我正在使用 Yageo 的 CC0603JRNPO9BN331 (330 pF±5% 50V 陶瓷电容器 C0G)。

我还尝试使用 X7R 电容器将电容器值更改为180pF/220pF/1nF、结果始终相同。

与封装0603有关、而不与电容器本身有关?

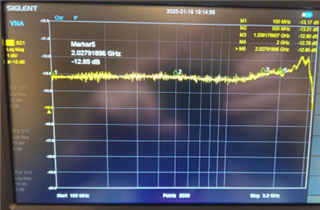

(下面的前端将进行调优以消除峰值、但即使我选择了响应非常平坦的电阻器、也具有相同的深度)

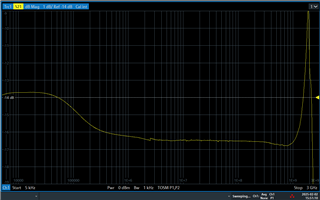

移除隔直流电容器:

在更改前端电阻器时也具有相同深度的示例。

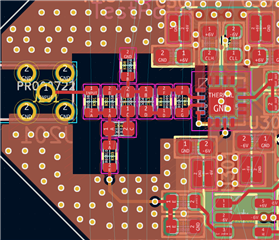

这是我们测试的布局: