主题中讨论的其他器件:OPA387、 OPA891、OPA814、OPA810

工具与软件:

简介

您好、TI 工程师和社区、

我是化学生物学实验室的一名实验室技术员、我擅长使用嵌入式系统进行硬件控制。 在我熟悉基本电路设计的同时、我主要使用数字电路、而且不熟悉模拟电路。 因此、我希望获得专家指导、以确保我的设计合理。 我非常感谢那些帮助我进行故障排除和改进此电路的人所付出的时间和精力。

项目概述

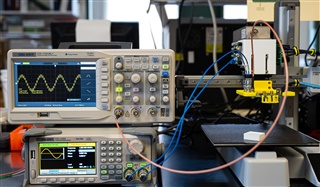

我们的实验室正在开发一种专用生物晶体管,它依赖于在两个电极之间精确桥接单壁碳纳米管(SWCNT)。 这是通过使用具有8 MHz、8Vpp 交流电场的电泳(DEP)来实现的、它会在电极上对齐纳微管。 为了防止多个纳米管桥接、我正在实现锁定放大、以检测纳米管何时成功完成电路。

检测方法(本出版物的 PDF 位于链接的 Google Drive 文件夹中)遵循已发布的方法、其中1kHz、100mVpp 的小交流基准信号叠加在8 MHz 信号上。 组合信号也具有较小的直流偏置。 但是、该研究论文没有披露电路拓扑、因此我设计了自己的模拟前端来生成所需的信号。

电路概述

我设计了一个模拟信号路径、这实现了以下目标:

-

电源:

- GoldPoint Level Controls 的 VG2电源提供分离轨虚拟接地系统(原理图标签:

EXTERNAL_PWR_VGND)。 - ADP7182 LDO 提供相对于

VGND的-2.5V 电压。 - ADP7102 LDO 提供相对于

VGND的+2.5V 电压。 2.5V 用于 OPA387偏置电压缓冲器。

- GoldPoint Level Controls 的 VG2电源提供分离轨虚拟接地系统(原理图标签:

-

偏置电压生成:

- 可调分压器和 OPA387电压跟随器可产生-2V 至 VGND 的偏置电压。

- 该偏置电压在加法放大器中反相、使其在最终输出中成为正偏置。

-

反相加法放大器(OPA891):

- OPA891电压反馈放大器对三个输入信号求和:

- 偏置电压(

Vbias来自 OPA387) - 8 MHz、来自的8Vpp 信号

AWG_1 - 来自的1kHz、100mVpp 信号

AWG_2

- 偏置电压(

- 由于采用了49.9Ω 端接电阻、所有输入信号均除以一半。

- 请求: 请验证 OPA891是否正确配置为对每个输入的增益为-1的所有输入求和。

- 示例计算:if

Vbias = -1V、VAWG_1 = -2V、和VAWG_2 = -1V、预期输出应为4V。

- 示例计算:if

- OPA891电压反馈放大器对三个输入信号求和:

-

有源缓冲器级(THS3491):

- THS3491高速运算放大器充当驱动高容性负载(~400 pF)的有源缓冲器。

- 负载电阻范围可能为数百 kΩ 至~1 MΩ。

- OPA891和 THS3491共享6.8 µF 的去耦电容、以提高空间效率。

- 请求:请验证 THS3491是否正确配置为增益为2的同相缓冲器。

- 此外、我希望获取有关我所选增益、反馈和隔离电阻器值的反馈(或是否存在更好的替代方案)。

-

LDO 功率验证(ADP7102和 ADP7182):

- 请求: 虽然我认为我的 ADP7102 (+2.5V)和 ADP7182 (-2.5V) LDO 配置正确、但我希望确认它们将在实施后提供稳定的输出电压。

- 如果 TI 工程师建议查看 Analog Devices、我很乐意这样做。

附件和设计注意事项(全部在链接的 Google Drive 文件夹中。)

- 原理图: 从 Fusion 360作为高分辨率 PNG 导出提供。

- 数据表: 随附相关元件数据表。

- 元件尺寸:

- 除钽电容器外、所有电阻器和电容器均为0805。

- 除非这会因寄生电感而严重影响运算放大器性能、否则我更倾向于保留该尺寸、以便于焊接。

- 如果考虑高频、则可以接受微小的谐波失真。 毕竟、我的目标频率低于10 MHz。

最后的想法

我非常感谢 TI 工程师和社区成员花时间审查我的设计并提供专业知识。 此项目是我的第一个复杂模拟电路、我希望确保我走在正确的轨道上。

请告诉我、我是否可以提供任何其他详细信息。 提前感谢您的见解! 如果没有犯过重大错误、我将开始规划 board.e2e.ti.com/.../E2E_5F00_Support_5F00_Docs_5F00_THS3491.zip 的布局

此致、

-Arjun