主题中讨论的其他器件: SysConfig

工具与软件:

尊敬的专家:

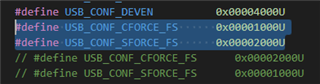

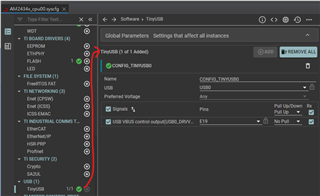

我们的团队 目前在 AM2434的 R5F0_0内核上使用 TinyUSB 通信时遇到问题(TinyUSB 是使用.SysConfig 配置的、如下图所示)。

在采用 SDK 8.6.0的非 OS 应用中、外部周期性 GPIO 用于触发 AM2434所有内核的 IRQ。 在 AM2434的 R5F0_0内核上、该周期性 IRQ 的优先级高于 USB 应用程序 IRQ 的优先级。

例如、如果 GPIO 触发周期为62.5 µs、则在正常情况下、AM2434的所有内核都将定期触发 IRQ 功能、而不会产生过多的延迟。

然而、当 R5F0_0内核通过 USB 模块连接到 PC 时、R5F0_0上的周期性 IRQ 触发时间偶尔会经历7到23 µs 的延迟(基于实验结果)。 在相同的触发时序下、AM2434的其他内核保持精确。 因此、我们认为 USB 模块的某些操作正在影响所有 IRQ 的触发。

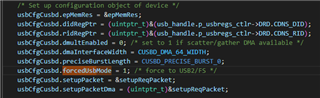

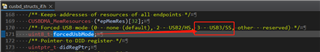

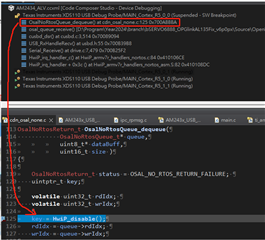

然后,我们在 SDK 8.6.0的 USB 源代码中发现,原始代码执行 Hwip_disable (),这会禁用所有的 IRQ 并导致延迟触发高优先级中断。下面描述了两个功能:

1. cdn_osal_none.c - OsalNoRtosQueue_enqueue()

2. cdn_osal_none.c - OsalNoRtosQueue_dequeue()

我们尝试重写这两个函数并删除HwiP_disable(),但问题仍然存在。

除了这两个函数,我们想知道 USB 源代码中是否有任何其他操作执行类似于HwiP_disable()或Semaphore_Pend()的操作,这可能导致所有中断触发被禁用。"

下面列出了程序中当前使用的 SDK 8.6.0函数:

- usb_wrapper.c

- usb_irq6_isr( )

- cusbd.c

- cusbd_dsr( )

- usbd.h

- tud_task()

- CDC_DEVICE.c

- TUD_CDC_n_Available( )

- TUD_CDC_n_READ( )

- TUD_CDC_n_READ_FLUSH( )

- TUD_CDC_n_WRITE_Available( )

- TUD_CDC_n_WRITE_FLUSH( )

- cdc_device.h

- TUD_CDC_n_WRITE_CHAR( )

专家能否帮助审查上述职能、并告诉我们哪些职能需要修改、或提供其他建议以解决这一问题?

此致

螺栓