请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM263P4 工具与软件:

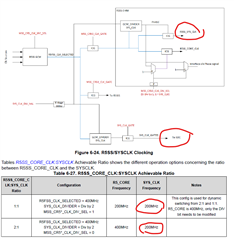

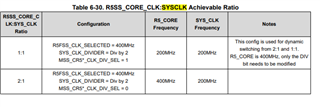

在所有 PWM 示例中、EPWM 为200MHz (XTAL=PWM 25MHz、400MHz、200MHz)。

为什么 SYS_CLK 不在400MHz 上? 请帮助解答以下问题:

- 将 SYS_CLK 设置为400MHz 是否有任何限制? (将 SYS_CLK_DIVIDER =除以1)

- 如何将 SYS_CLK 设置为400MHz?

- 我是否需要拥有新的 SBL?

- 为了完整起见、EPWMCLK 也不能作为400MHz 的原因是什么吗?

其他相关问题:

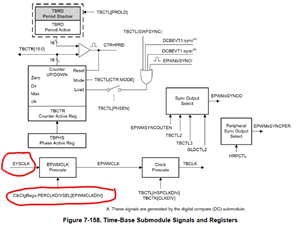

- 在 TRM 的图7-158中、EPWMCLK 源自哪个 SYSCLK? 请参阅图6-24

- R5SS_SYS_CLK 或 SYS_CLK_GATE。

- 在图7-158上、在哪里可以找到寄存器"ClkCfgRegs.PERCLKDIVSEL[EPWMCLKDIV]"来配置 EPWMCLK 预设?

- 通过搜索 SDK 代码和 Register Addendum.pdf 无法找到任何令牌/字

提供我的问题的一些图片以提供帮助。

感谢您的支持。