工具与软件:

我需要将 hex 文件加载到 RAM 中进行固件升级和从 RAM 引导,您能帮助我在链接器文件中进行更改吗

对于引导加载程序的 VTABLE 部分、并为固件升级十六进制文件写入 hex 文件并从中进行引导使用 RAM

当我尝试在分配用于执行的存储器区域之外的空间中写入 RAM 段时、它仅写入"0"零。

您能否建议如何为 应用 VTABLE 部分对 RAM 进行分区以及 通过以太网写入固件升级十六进制文件。

您还可以查看链接器文件以了解要进行的任何更改吗

/******************************************************************************

* Copyright (c) 2013-2017 Texas Instruments Incorporated. All rights reserved.

* Software License Agreement

*

* Texas Instruments (TI) is supplying this software for use solely and

* exclusively on TI's microcontroller products. The software is owned by

* TI and/or its suppliers, and is protected under applicable copyright

* laws. You may not combine this software with "viral" open-source

* software in order to form a larger program.

*

* THIS SOFTWARE IS PROVIDED "AS IS" AND WITH ALL FAULTS.

* NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT

* NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE. TI SHALL NOT, UNDER ANY

* CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR CONSEQUENTIAL

* DAMAGES, FOR ANY REASON WHATSOEVER.

*

*

*****************************************************************************/

--retain=g_pfnVectors

/* The following command line options are set as part of the CCS project. */

/* If you are building using the command line, or for some reason want to */

/* define them here, you can uncomment and modify these lines as needed. */

/* If you are using CCS for building, it is probably better to make any such */

/* modifications in your CCS project and leave this file alone. */

/* */

/* --heap_size=0 */

/* --stack_size=256 */

/* --library=rtsv7M3_T_le_eabi.lib */

/* The starting address of the application. Normally the interrupt vectors */

/* must be located at the beginning of the application. */

#define APP_BASE 0x00000000

#define RAM_BASE 0x20000000

#define RAM_BASE_DATA 0x20007000

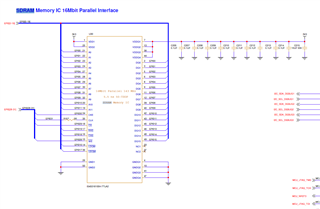

#define EX_RAM_BASE 0x60000000

#define APP_LENGTH 0x00016000

/* System memory map */

MEMORY

{

/* Application stored in and executes from internal flash */

FLASH (RX) : origin = APP_BASE, length = APP_LENGTH

/* Application uses internal RAM for data */

SRAM (RWX) : origin = RAM_BASE, length = 0x00060000

EXSRAM (RWX) : origin = EX_RAM_BASE, length = 0x00040000

}

/* Section allocation in memory */

SECTIONS

{

.intvecs: > APP_BASE

.text : > FLASH

.const : > FLASH

.cinit : > FLASH

.pinit : > FLASH

.init_array : > FLASH

.vtable : > RAM_BASE

.data : > SRAM

.bss : > SRAM

.sysmem : > SRAM

.stack : > SRAM

.vtable : > EX_RAM_BASE

.data : > EXSRAM

.bss : > EXSRAM

.sysmem : > EXSRAM

.stack : > EXSRAM

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

.TI.ramfunc : {} load=FLASH, run=SRAM, table(BINIT)

.TI.ramfunc : {} load=FLASH, run=EXSRAM, table(BINIT)

#endif

#endif

}