工具与软件:

OSPI 连接到闪存、并与单个 I/O 总线一同使用。

OSPI 仅在引导期间读取。

该程序旨在仅在插入 USB 时才将 USB 数据写入闪存。

当前、由于未插入 USB、因此在引导后无法访问。

在这种状态下、如果电源关闭、则可能存在 OSPI 访问。

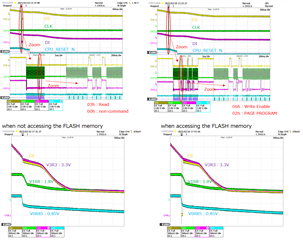

我在断电期间用一个示波器检查了被发送至闪存存储器的命令。

在大多数情况下、该命令为读取命令(03h)或 (00h)。

在极少情况下、发送写入使能命令(06h)和页编程命令(02h)。

由于页面程序在断电期间发生、因此会在中途切断电源、并且闪存中的数据会损坏。

在访问闪存或不在断电期间、电源电压似乎没有差异。

问题1。 在断电期间、CPU 是否不可避免地发生故障并访问闪存?

如果在断电期间执行读取命令、则不是问题。 但是、我希望避免执行页面程序。

问题2: 是否有办法避免这种情况?