工具与软件:

您好!

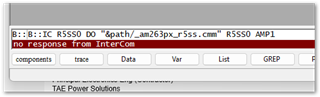

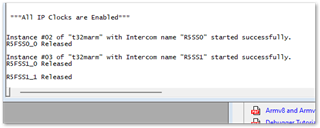

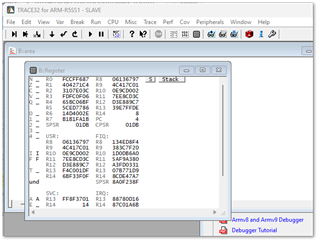

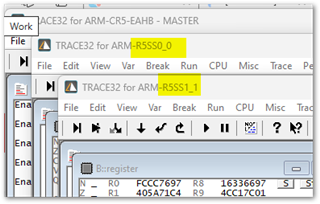

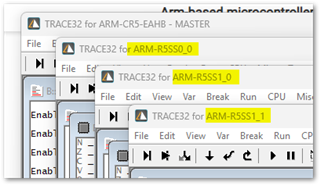

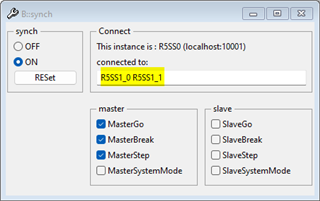

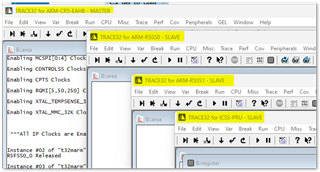

我运行了"_am263px_allcoretype_connect.cmm"脚本、期望在适用于 ARM-R5xxx 的四个 TRACE32实例中看到该脚本。 但是、我只能得到以下信息:

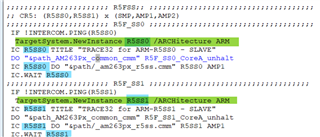

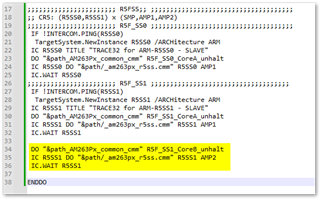

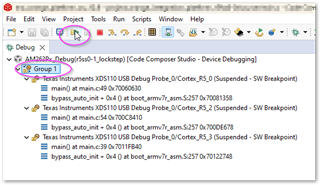

我的工程为 R50_0、R51_0和 R51_1。 (R50_1处于锁步模式)。

我想对 R50_0、R51_0和 R51_1使用 Data、load.Elf。

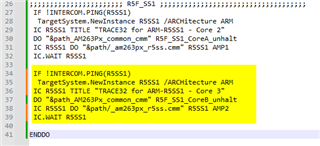

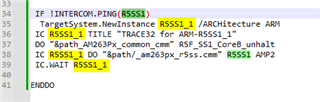

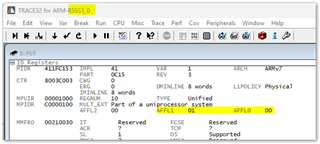

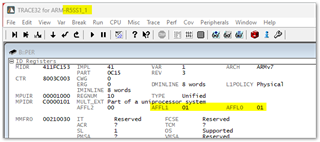

- "ARM-R5SS0"= R50_0且"ARM-R5SS1"= R51_0、正确吗?

- 如果是、为了加载其.out 文件、R51_1的实例在哪里?

- 如果没有、请更正我的误解。

谢谢你。