主题中讨论的其他器件: SysConfig

工具与软件:

尊敬的专家:

(AM2434 + S28HL512T)

闪存数据表:

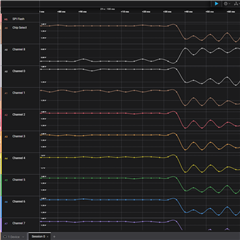

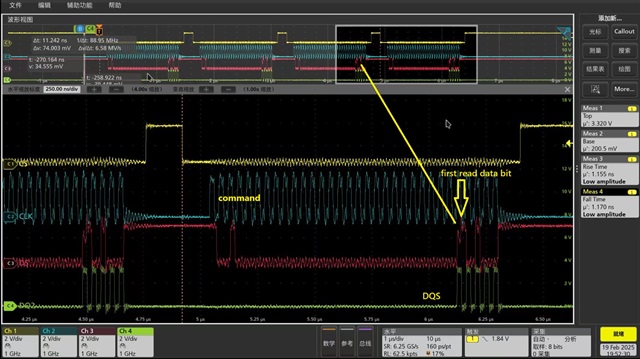

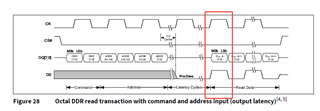

在8D 模式下读取 OSPI 闪存时的波形、发现 DQS 引脚的高电平未到达第一个数据位处的 VDD、如下图所示。

对应于以下标记。

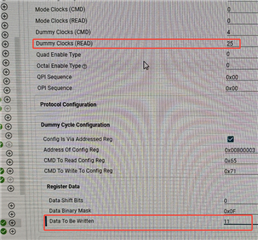

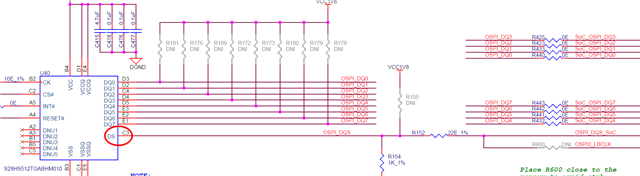

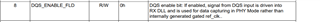

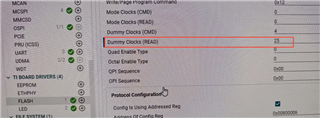

我们认为这 可能是由于 SysConfig 的此配置值造成的

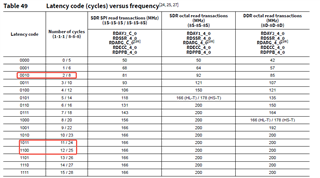

通过 ospi_flash_diag 项目、我们可以从闪存芯片中读取 dummyClksRd = 24、 它恰好比 SysConfig 值低一个时钟。

主机延迟了 CLK 释放 DQS 引脚的时间、导致出现半电平?

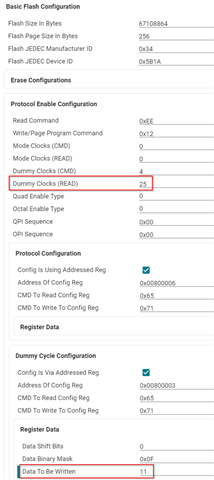

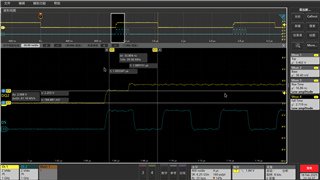

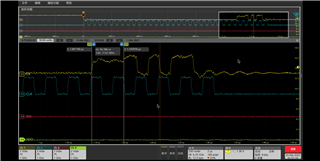

在测试时、将该值更改为26、 然后再扩展一个 CLK 半电平、如下图所示。

然后 更 改为24、无法正确从闪存读取值。

现在我们想问一下我们的猜测是否正确、如何消除这个半层次的问题?