工具与软件:

大家好:

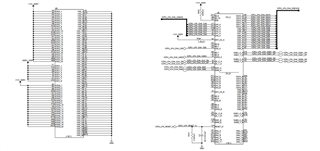

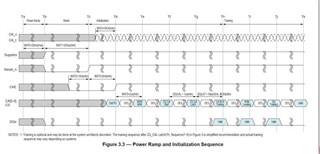

我们的项目 AM2432外部扩展 RAM 为 LPDDR4模型:IS43LQ32256B-062BLI 和 ISSI、我们发现、在 DDR"电源斜坡和初始化序列"与 LPDD4手册不一致的情况下、Reset-n 将 DDR 的 CKE 信号拉高后、DDR 的 CKE 信号有一个短暂的高脉冲信号(10us)、请帮助确认该信号的原因以及其是否合理。

注意:

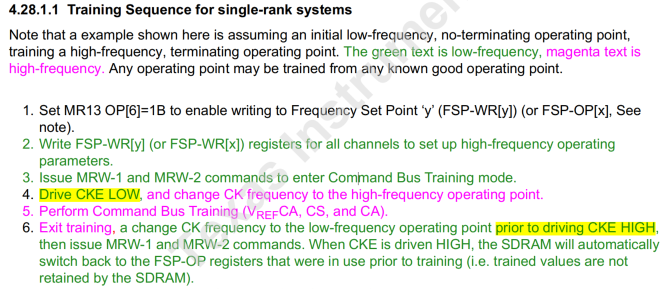

图1 LPDDR4电源斜升和初始化序列

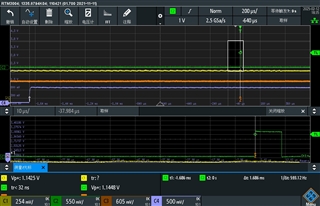

图2功率斜升和初始化序列示波器的实际测试波形

图1 LPDDR4电源斜升和初始化序列(来自数据表)

图2 LPDDR4电源斜升和初始化序列(WE 测试范围)