主题中讨论的其他器件:SYSCONFIG、 AM2634、AM263P4、 UNIFLASH

工具/软件:

您好:

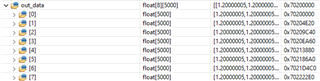

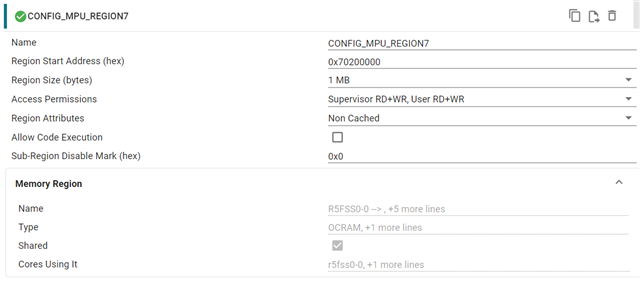

我尝试使用0x7020 0000到0x702F FFFF 的存储器区域作为共享存储器。 由于没有任何示例在 MPU 中定义该区域、因此我在 SysConfig 中添加了一个条目、如下所示:

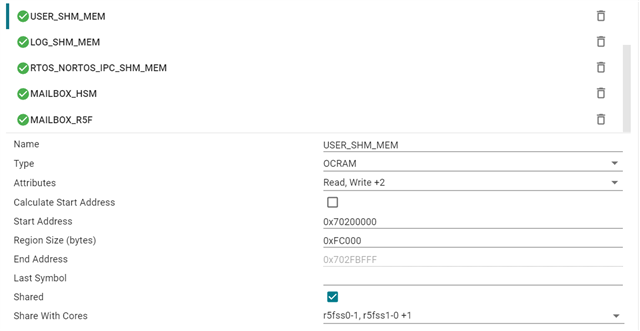

然后在存储器区域中、将其设置为 Shared:

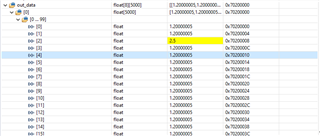

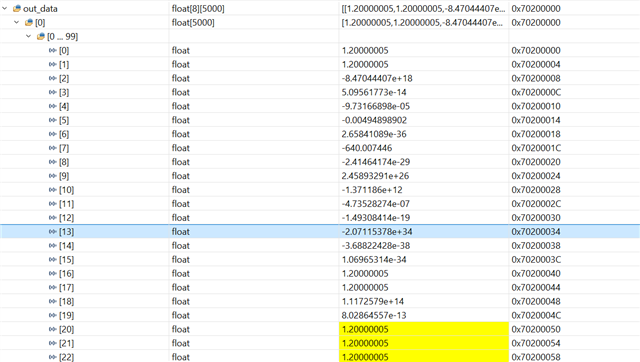

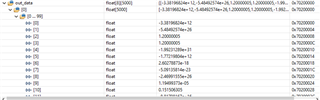

在代码中、我有一个定义如下的变量:

#define OUTPUT_BUFFER_LENGTH 5000

#define ANALOG_CHANNES_PER_CORE 4. volatile float out_data[ANALOG_CHANNELS_PER_CORE * 2][OUTPUT_BUFFER_LENGTH]__attribute__((section(".bss.user_shared_mem")));

然后我尝试将数组初始化为0:

for(uint16_t i = 0; i < (ANALOG_CHANNELS_PER_CORE * 2); i++) { for(uint16_t j = 0; j < OUTPUT_BUFFER_LENGTH; j++) { out_data[i][j] = 0.0f; } }

问题不是所有值都设置为0、如果我暂停应用程序并尝试手动将数组值设置为0、它仍然不起作用! 我想知道这是否是器件问题? 我有坏的 SOC 吗? 或配置问题?

更新:我测试了另一个主板并得到了相同的结果、所以这不是一个糟糕的 SOC。