工具/软件:

尊敬的 TI 专家:

在最新的 SDK9.2版本手册中、我们发现有一些优点 2重要修复 PLL 序列的计算示例。

修复1:

修复2:

实际上、客户已经将 SDK9.1用于大规模生产。 客户想知道上述两个 PLL 问题对仍使用 SDK9.1的影响是否与以下勘误表相同?

客户希望知道他们是否可以在 SDK9.1上针对上述两个修复程序提供补丁、这样他们就不需要完全升级到 SDK9.2、只需要 PLL 修复。

谢谢、

Kevin

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的 TI 专家:

在最新的 SDK9.2版本手册中、我们发现有一些优点 2重要修复 PLL 序列的计算示例。

修复1:

修复2:

实际上、客户已经将 SDK9.1用于大规模生产。 客户想知道上述两个 PLL 问题对仍使用 SDK9.1的影响是否与以下勘误表相同?

客户希望知道他们是否可以在 SDK9.1上针对上述两个修复程序提供补丁、这样他们就不需要完全升级到 SDK9.2、只需要 PLL 修复。

谢谢、

Kevin

Σ-Δ 来自 SDK 09.01.00.06 -单核无负载共享(ICSSG1 PRU1)

请查看 RAM 的最后一条评论-该评论解决了此标签中描述的问题

此外:

我们正在做以下工作:

/*配置 SYNCI/SYNCO 映射、以将三个 PWM 组绑定在一起并使 PWM0同步来自时间同步路由器38 */

CSL_REG32_WR (CSL_CTRL_MMR0_CFG0_BASE+CSL_MAIN_CTRL_MMR_CFG0_EPWM0_CTRL (2<CSL_MAIN_CTRL_MMR_CFG0_EPWM0_CTRL_SYNCIN SEL_SHIFT);

/*时间同步路由器输入25 (ICSSG1 IEP0 SYNC0)->时间同步路由器输出38 (0x26 + 4 = 0x2A +时间同步路由器基址*/

CSL_REG32_WR (CSL_TIMESYNC_EVENT_INTROUTER0_CFG_BASE +((38 * 4)+ 4)、(0x10000 | 25));

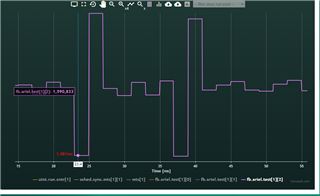

请查看以下图片:

在这里、您可以看到一个软件测量值、它显示了每个 Sync0任务之间经过的时间。

ECAT 周期时间为2ms。

您可以看到信号周围有抖动、偶尔大约为15uSec 时会出现非常大的抖动。

另请注意、第一个抖动是一个较短的呼叫、然后似乎它会通过延迟进行补偿。

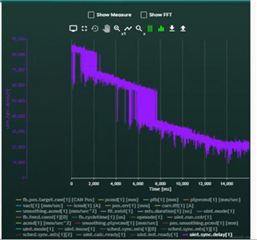

在这里、您可以看到 Sync0 SW ISR 信号与 Σ-Δ ISR 调用之间的时间差记录。

您可以清楚地看到、随着时间的推移、会出现漂移

尊敬的 Ariel:

我想您在错误的主题中提供了详细信息。 您可能需要输入以下主题以讨论 SYNC0。

谢谢、本主题主要讨论 PLL 修复。

Kevin

您好 Kevin

Unknown 说:实际上、客户已将 SDK9.1用于大规模生产。 如果客户仍使用 SDK9.1、他们想了解上述两个 PLL 问题的影响是否与以下勘误表相同?

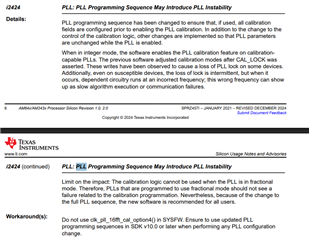

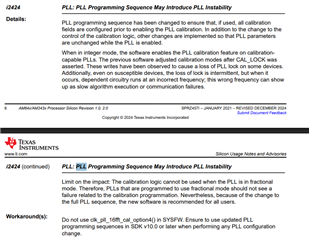

没有简单的方法可以客观地量化 PLL 勘误表的影响。 请参阅 i2424说明中的以下内容。

此外、即使在易受影响的器件上、锁定的丢失也是间歇性的、但在这种情况下

发生时、依赖电路的运行频率不正确;可能会出现这个错误的频率

缓慢算法执行或通信故障。

建议通过将 SYSFW 版本更新至 SDK10.0或更高版本来修复此勘误表。 它们应向后兼容、并可通过参考 RTOS SDK 中的以下开发人员手册进行更新。

此致

Karan

您好 Kevin

这同样适用于 AM243、并记录在 AM243文档中。

此致

Karan