请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSPM0G3507 主题:SysConfig 中讨论的其他器件

工具/软件:

您好、

目前我正在尝试使用 VREF 模块来配置 ADC 的外部基准电压。

1)如何配置这个寄存器为采样保持?

2)为什么我们甚至需要采样保持?

提前感谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

目前我正在尝试使用 VREF 模块来配置 ADC 的外部基准电压。

1)如何配置这个寄存器为采样保持?

2)为什么我们甚至需要采样保持?

提前感谢

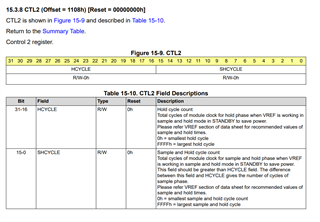

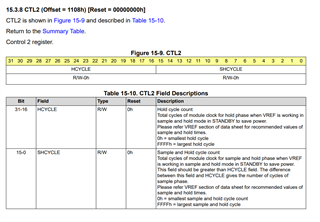

采样保持模式支持在 STANDBY 工作模式下运行 VREF、因此如果您需要使外设的 VREF 处于超低功耗模式、可以使用这种模式。 如果您想启用采样保持功能、一种配置采样保持功能的更简单方法是通过 SysConfig。 我从 SysConfig GUI 中概述了这些参数。 如果您只想使用内部/外部 Vref 而不进行采样保持、您也可以在 SysConfig 中启用它。

The recommended sample time is >30us waiting for VREF to stabilize.

The timing is calculated as:

Sample_time =Sample_cycles/VREF_Clock

Where:

VREF_Clock = VREF_Clock_Source/VREF_Clock_Divider

(See Clock Configuration section for more details).

Sample_cycles = 0 to 65535.

If VREF_Clock is 32.768kHz (i.e. LFCLK), and Sample_cycles = 1, the resulting Sample_time will be ~30.51us.

Hold time should be such that the accuracy degradation due to leakage is within

DAC acceptable limits. The recommended hold time is 6ms.

The timing is calculated as:

Hold_time = Hold_cycles / VREF_Clock

Where:

VREF_Clock = VREF_Clock_Source/VREF_Clock_Divider

(See Clock Configuration section for more details).

Hold_cycles = 0 to 65535.

If VREF_Clock is 32.768kHz (i.e. LFCLK), and Hold_cycles = 197, the resulting Sample_time will be ~6.01ms.