工具/软件:

您好、

我想使用内部振荡器生成80 MHz 时钟。 我以前使用过以下配置:

2个问题:

- 是否建议在不使用外部振荡器的情况下在80 MHz 上为 MCU 提供时钟?

- 通过 PLL 时的精度(数据表中的7.9.1.1 SYSOSC 典型频率精度)是否受到影响?

谢谢、

Geoffrey

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我想使用内部振荡器生成80 MHz 时钟。 我以前使用过以下配置:

2个问题:

谢谢、

Geoffrey

Unknown 说:是否建议在不使用外部振荡器的情况下在80 MHz 上为 MCU 提供时钟?

您正在使用 sysosc 来获取 syspll 的源代码。

您的配置正确、请参阅数据表 7.9.3系统锁相环(SYSPLL)

以下是我这边的配置:

e2e.ti.com/.../7043.empty.syscfg

Unknown 说:通过 PLL 时精度(数据表中的7.9.1.1 SYSOSC 典型频率精度)是否受到影响? [/报价]是的。

因为 sysosc 是 syspll 的来源。

您是否确认这是尽可能提高准确性的最佳配置? [/报价]精度主要基于 SYSOSC。

您可以使用外部 ROSC 启用 SYSOSC 的 FCL 功能。

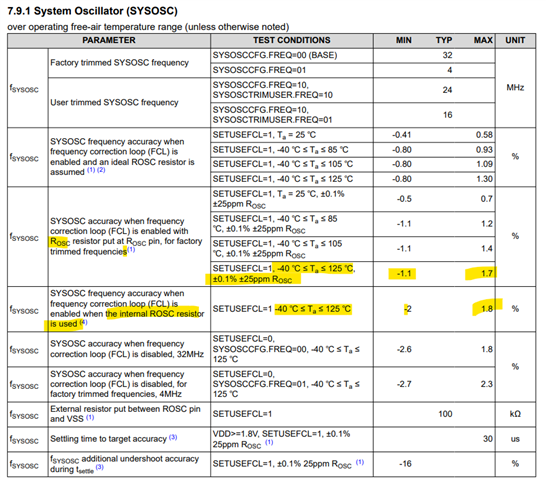

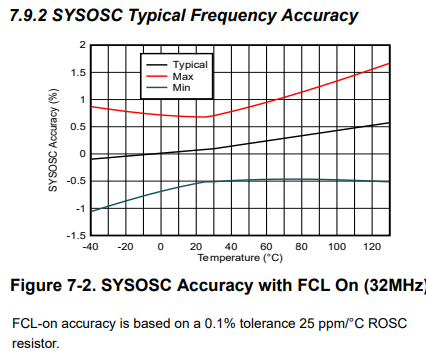

有关 FCL 精度、请参阅数据表- 7.9.1系统振荡器(SYSOSC)- 在 ROSC 电阻器置于 ROSC 引脚的情况下启用频率校正环路(FCL)时的 SYSOSC 精度、用于经过出厂修整的频率

2)我很难理解如何确定 PLL 输出的精度、您能 详细说明吗?时间精度主要基于 SYSOSC 的精度。

[/quote]

您好、

是的、我看到了这些信息、这些信息是一致的。

更具体地说、我需要在-40至125°C 的整个温度范围内实现小于+/-2%的总精度。

1)使用外部 ROSC 似乎可以提供足够的裕度

2)也可以选择使用内部 ROSC、但没有裕量。 您说过精度主要取决于 SYSOSC、但在本例中 、我仍需要了解 PLL 将如何影响精度 、以确定选项2是否可行。 PLL 是否会将误差增加至+/-0.1%? 小于此值?

此致

Geoffrey

这与 PLL 本身有关。

PLL 是否会将误差增加到+/-0.1%? 小于?

在正常工作状态或 PLL 锁定状态下、SYSPLL 输出时钟将跟随输入时钟基准(SYSOSC)、这会给 SYSPLL 增加一些抖动、而精度也在 SYSOSC 之后。

我不是 PLL 的专家、我认为 SYSPLL 不会使误差增加到0.1%以上、因为抖动误差本身将在锁定相位内保持在100ps 以内。

我方面的另一个提示、请尝试将 VCO 设置为160MHz。