工具/软件:

您好、

请查看我的时序分析。

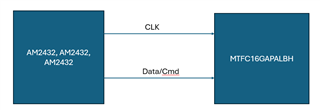

我们计划在即将开展的项目中使用以下器件。

SoC:

旧 SDR 模式:

Tclk (MMC0)= 40ns

TD= Tclk-dV 或 Tclk-cmd = min (-2.3ns)、max (2.9ns)

eMMC:符合 JEDEC 标准

(min)= 3ns

(min)= 3ns

Toutput_delay (最小值/最大值)= 2.5ns/13.7ns

假设 SoC 正在驱动时钟和命令、在这种情况下、我们将进行以下时序分析

td + Tpcb_data_delay (max) < tpcb_clk_delay + Tclk ------ EQ1

Tpcb_data_delay (max) - Tpcb_clk_delay < Tclk - Tsetup_eMMC–td

tpcb_data_delay (max) - tpcb_clk_delay < 40-3-2.9

Tpcb_data_delay (max) - Tpcb_clk_delay < 34.1ns

td + Tpcb_data_delay (min)> thold_eMMC + tpcb_clk_delay ------------------- eQ2

tpcb_data_delay (min)- tpcb_clk_delay > thold_eMMC - td

tpcb_data_delay (min)- tpcb_clk_delay > 3-(-2.3)

Tpcb_data_delay (min)- Tpcb_clk_delay > 5.3ns

这意味着相对于时钟、数据或命令跟踪延迟应在5.3ns 到34.1ns 之间。

假设标准 PCB 布线延迟为150ps/in、要实现5.3ns 延迟、则需要将布线比时钟布线长约35英寸、这显然不切实际。

我觉得我可能在这里遗漏了一些东西。 您能帮助澄清一下吗?

任何 TI 文档中是否提供了任何 eMMC 布线指南以及偏斜详细信息?