工具/软件:

你好。

我有 SPI RX 和 TX DMA 同时工作。

它似乎基本上能正常工作、但我显然收到了一个错误、我认为是 RX FIFO 和 DMA 问题导致的数据。

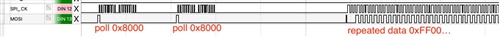

RPI 通过连续发送0x8000来轮询 MCU。

当 MCU 轮询时、它以轮询进行响应、然后通过 DMA 传输 TX 数据。 这种方法很有效。

由于 SPI 通过 DMA 同时是双工 I RX 数据。

数据 RX 数据固定在0xf0f0、因此我可以看到正在发生什么。

但是、 RX 数据的前两个数据包被"轮询"破坏??

RPI 发送的数据正确、我可以在逻辑分析仪上看到这一点、请参阅 snip。

NB -由于各种原因、我在轮询和数据之间更改 SPI 时钟速度、这一切都可以正常工作。

进行以下设置和两次剪切。

NB - MOSI 存在一个不是最后一次轮询后的真实数据的干扰(宽度为10ns、不产生影响)。

有任何线索?? 似乎很接近、一如既往的…

--

Phil