工具/软件:

尊敬的 Shaunak:

我想 为 IPC 使用2个内核、并且还需要启用锁步功能、因此请告诉我如何为我的工程启用锁步和 IPC

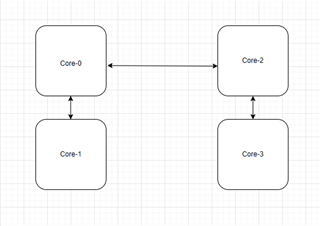

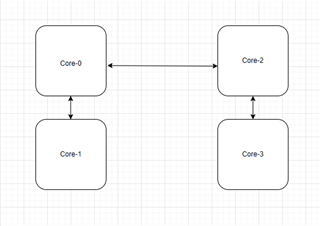

核心实现如下所示

2.如果 Cortex M4_0有4个内核,它的用途是什么

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的 Shaunak:

我想 为 IPC 使用2个内核、并且还需要启用锁步功能、因此请告诉我如何为我的工程启用锁步和 IPC

核心实现如下所示

2.如果 Cortex M4_0有4个内核,它的用途是什么

您好 Rohal。

[报价 userid="564990" url="~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1519299/am2634-ipc-communication-configuration-and-lockstep-configuration我想 为 IPC 使用2个内核、并且还需要启用锁步功能、因此请告诉我如何为我的工程启用锁步和 IPC

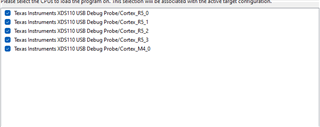

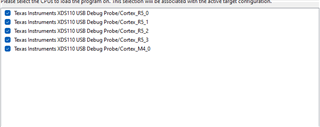

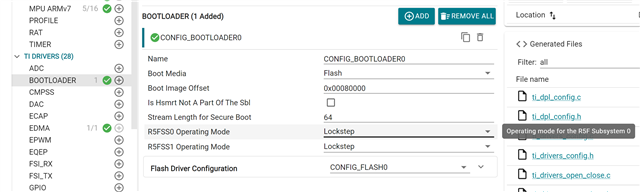

[/报价]您可以通过 SBL 应用的 example.syscfg 在锁步和双核模式之间切换。 假设您使用 SBL-QSPI 刷写应用程序、然后在"Bootloader"部分中、您可以选择 R5F 集群配置、在这种情况下、两个集群都将处于锁步模式。

在使用此 Re 的 tiimage 刷写应用程序之前、先编译 SBL

或者、您也可以通过 GEL 脚本(使用开发引导模式)对此进行配置、请参阅 GEL 部分的此常见问题解答(对于 SBL 部分、请按照上述步骤操作、因为我们现在可以选择从 syscfg 中选择模式)

[报价 userid="564990" url="~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1519299/am2634-ipc-communication-configuration-and-lockstep-configuration2.如果 Cortex M4_0有4个内核,它的用途是什么

[/报价]M4内核专用于安全相关功能(硬件安全管理器或 HSM)。 M4内核不能直接用于运行用户应用程序。 M4内核从初始 ROM 引导加载程序开始使用、直到实现应用程序运行时安全性以及其他安全产品。

除此之外、对于用户应用、还有2个 PRU 内核(一个 PRU-ICSS 实例的一部分)和4个 R5F 内核。

此致、

Shaunak