工具/软件:

对于 CTI –20 引脚排列、引脚 5 VTRef。 我在我所在的公司找到了一些内部文档、这说明器件内部的这个引脚上有一个 100Ω+二极管下拉电阻器。 在用户手册或应用手册中找不到调用此电路的任何信息。 想确认该引脚的内部电路是什么样的、如果没有下拉电路、则此引脚上的预期电流消耗是多少?

感谢你能抽出时间。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

对于 CTI –20 引脚排列、引脚 5 VTRef。 我在我所在的公司找到了一些内部文档、这说明器件内部的这个引脚上有一个 100Ω+二极管下拉电阻器。 在用户手册或应用手册中找不到调用此电路的任何信息。 想确认该引脚的内部电路是什么样的、如果没有下拉电路、则此引脚上的预期电流消耗是多少?

感谢你能抽出时间。

您好、Josh、

您是指该电路位于调试器本身的内部、还是位于调试器中实现的 IC 的内部?

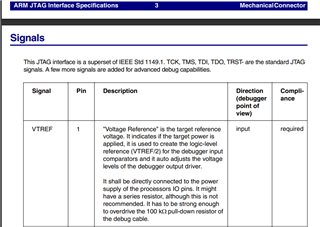

我将提供 VTREF 引脚的快速说明以供参考。 也就是所谓器件内部时的消隐时间。

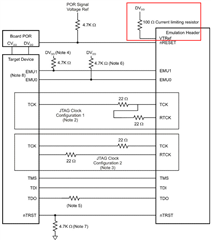

我在此处无法找到有关二极管连接的任何详细信息、但典型的 JTAG 仿真器电路 需要 100Ω 上拉 电阻器。 需要通过限流电阻将信号上拉至目标器件所需的电压源电平。

该引脚上的电流消耗是设计到调试器硬件中的 IC 的一个特性。 我正在与其他几位团队成员联系、尝试在此处找到答案。

此致、

Zackary Fleenor

感谢您发送编修。 我对从 VTREF 引脚到调试器电缆以及调试器本身中的任何内容的整个电路路径很好奇。 在我们的设计中、我们在此引脚上有一个外部 100Ω 上拉电阻器(根据建议)、我需要确保我们针对它将经历的压降和功耗调整合适的大小。

感谢您查看此引脚上的电流消耗、这将是非常有用的信息。 从第一个调用 VTREF/2 的屏幕截图中的说明开始、要求该引脚上拉至处理器的 IO 电源、并使用第二个屏幕截图中建议的 100Ω 上拉电阻。 这是否意味着调试器内部某个位置必须有一个 100Ω 下拉电阻器以创建该分压 (VTREF/2)? 只是尝试在调试器中的某个位置拼凑起来、在这里我们得到了这个假设(在我公司)用于 100Ω 下拉电阻。

此致、

- Josh

你好 Josh、

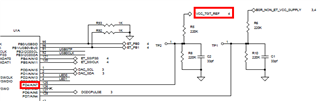

我在这里做了更多的挖掘。 VTREF/2 信号馈送到 TM4C1294 器件的典型 ADC 通道 (AIN7)。 PCB 设计中已经有 2 个 220kΩ 电阻器、用于产生 2 分压、同时满足前面所述的“足够强、能够过驱电缆的 100kΩ 下拉电阻器“标准。 我没有意识到有任何其他 与 VTREF 引脚/信号搭配使用的 100Ω 下拉。

此致、

Zackary Fleenor