工具/软件:

您好:

我想澄清有关 静态配置寄存器定期软件回读的预期寄存器定期检查。

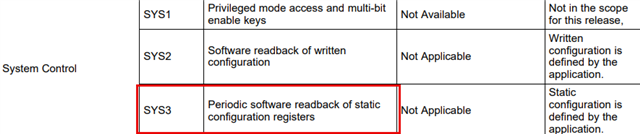

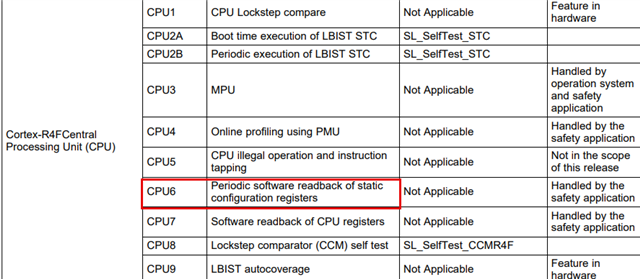

我知道这些测试与有关分区系统控制和 CPU 的配置寄存器检查有关、这些检查不应在软件运行时修改。 我想确保这些测试不会相互重叠。

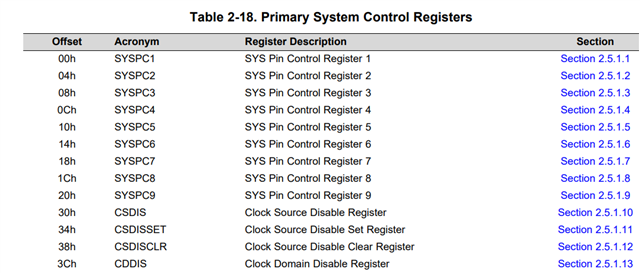

然后、我想 SYS3 安全机制“直接“在 TMS570 技术手册 (SPNU499C) 中找到要检查物理地址的系统寄存器。 (下面的寄存器示例)

然后是 CPU6 请求的安全机制、我想在这里确认 “内部“寄存器的预期寄存器检查处于 Arm CPUR4F 级别。

我的理解是、这里我们讨论了要检查的 CPU 寄存器、而 SYS 检查不能涵盖这些寄存器。

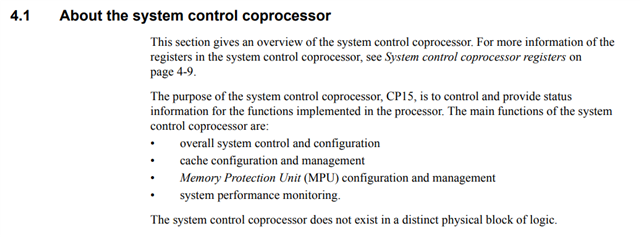

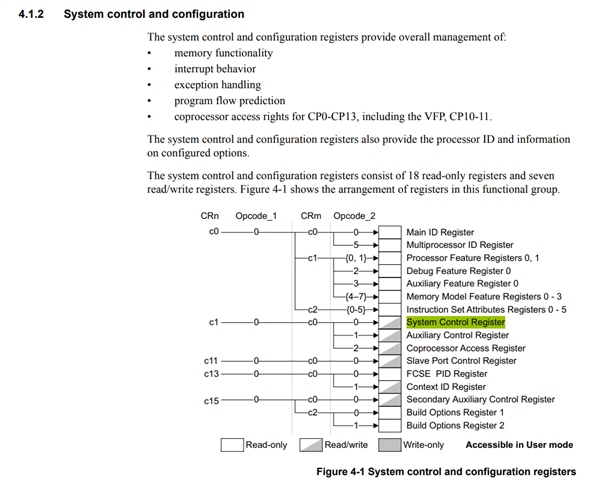

根据 Cortex -R4 和 Cortex-R4F 修订版:r1p3 技术参考手册 第 4 章系统控制协处理器、显示了如何对内部 CPU 设置进行编程和检查。

还有一些不同的寄存器被描述为 系统控制寄存器、并具有写入和读取功能:

我可以看到、这些核心 CPU 寄存器 在由函数(通过汇编指令)提供的早期 MCU 启动时进行配置。 这些命令从 SafeTi 库设置或通过卤素工具生成进行配置。

我的问题:

CPU6 测试的目标是否是定期读取这些 CPU 寄存器(不应更改)的确定数量(取决于系统要达到的安全级别)?

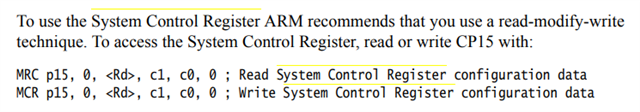

如果是、 我们是否需要使用汇编指令来实现某些函数以读取 Cortex -R4 和 Cortex-R4F 修订版:r1p3 技术参考手册中所述的值? (因为与 SYS3 测试一样、此功能无法通过映射的 MCU 系统控制寄存器进行访问)

感谢您的澄清、

此致、

Marc