请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSPM0C1104 工具/软件:

尊敬的 TI 团队

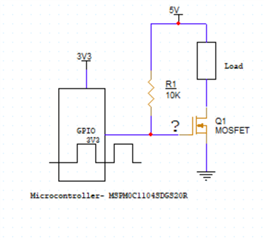

请在下面找到图片。 我们将一个负载连接到微控制器、如下所示。 由于我们允许负载在已知状态下工作、因此我们将在 FET 的栅极添加一个上拉电阻器 (10K)。

由于 I/O 能够承受 5V 电平、因此微控制器连接到 3V3 内核、上拉电阻连接到 5V。

当 FET 的输入为低电平时、栅极电压较低。

在 FET 的输入为高电平期间、栅极接收到的电压的振幅电平是多少 (5V/3V3)? 请澄清。

此致、

Murugavel.S.