工具/软件:

我在航空航天领域有一款使用 AM2434 芯片(现场安全型号)的新产品。 由于认证限制、我们选择通过执行安全交付操作来禁用 DMSC。 因此、我们现在要为系统控制功能编写自己的驱动程序。 我理解、这不是 TI 的建议。

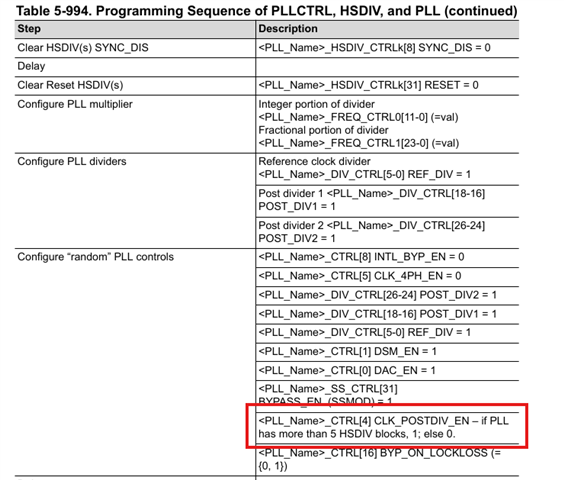

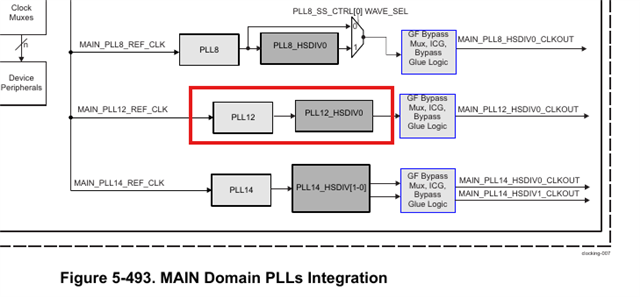

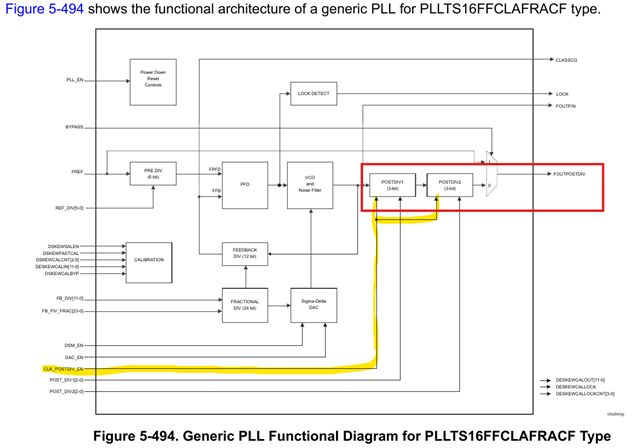

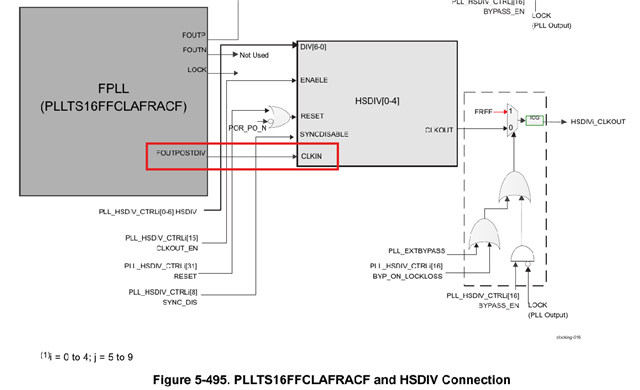

当前我正在尝试为自定义 SBL 启用 DDR 接口、因此遇到令人费解的行为。 按照 TRM、AM243x SDK 和 TI GEL 文件、我能够复制 MPU、PLL 和 PSC 控制器以开始启用系统硬件。 问题是 EMIF_CFG_0 模块域的 LPSC 控制器。 我可以启用芯片中除该电源/模块域之外的所有电源/模块域。 我甚至可以启用 EMIF_DATA_0 模块、尽管 TRM 声称在启用 EMIF_CFG_0 域之前我无法启用该模块。

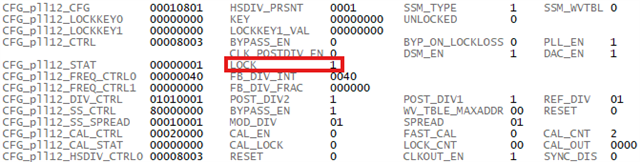

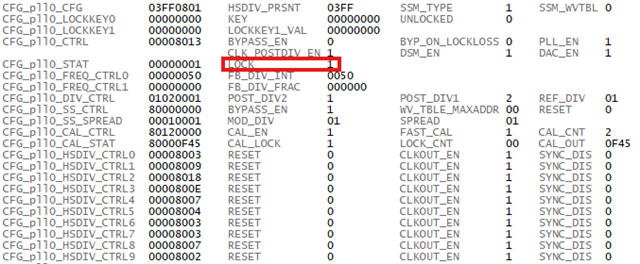

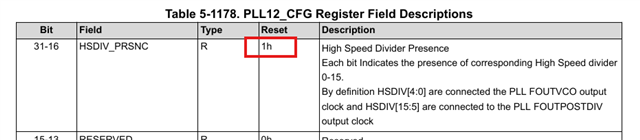

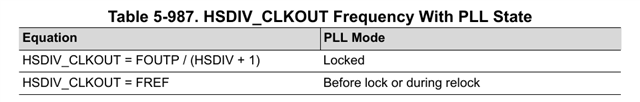

我配置了电源转换的设置、发出 GO 命令、然后挂起等待 GOSTAT 清除。 重申一下、同一个驱动程序适用于所有其他模块域。我已根据 TI GEL 文件 (AM24_PLL_Params_OFC1.gel) 启用/配置了系统中的所有 PLL(MCU 除外)、我知道由于自动时钟门控功能、这是对 LPSC 模块正确使用的依赖。

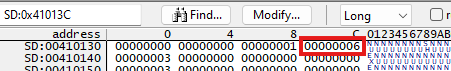

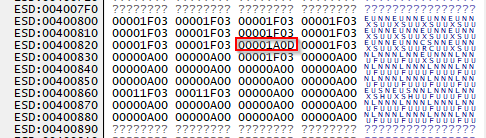

我在系统 MD_STAT 寄存器块中观察到的是、我配置的所有模块域都最终处于“良好“状态 0x1F03、但 EMIF_CFG_0 域结束于 0x1A0D、这似乎与 SDK 中列出的枚举值没有任何意义。

我在这里遗漏了什么? 我可以启用 emif_data_0 域但不启用 CFG 域、这感觉不可思议地奇怪。 通过所有的外观,这两个连接在一起,因此满足其中一个的“打开“依赖关系应该启用另一个。