工具/软件:

我可以在 GPIO 触发器正边沿上同时转换正常运行的 ADC。 一切都很好。

我写入引脚 CCK、这将开始转换。

我想知道它何时完成,然后我开始下一次转换....这只是挂起:

while (1){

}

有任何线索请?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我可以在 GPIO 触发器正边沿上同时转换正常运行的 ADC。 一切都很好。

我写入引脚 CCK、这将开始转换。

我想知道它何时完成,然后我开始下一次转换....这只是挂起:

while (1){

}

有任何线索请?

你好。

我的错误...标记已设置...先清除。

这似乎有效:

//触发 ADC 转换

DL_GPIO_setPins (GPIO_SA3_CCK_PORT、GPIO_SA3_CCK_PIN);

//等待完成

DMA 清除 DMA_TRIG:RIS:MEMRESIFG0、但不清除 CPU_INT:RIS:MEMRESIFG0【观察到的行为】。 要使用此机制、您需要在发出 CCK 触发器之前清除前者(我认为这就是您所说的操作?)。

还有 status:busy (DL_ADC12_getStatus ())、从描述中可以或多或少地按照您期望 SC 的行为方式进行操作。 (我没有试过。) 我预计这将 容易受到与之前相同的种族(TRIGGER 和第一次 getStatus 调用之间的杂散中断)的影响。

[编辑:您是否有用于 dma_done 的 ISR(即,这会将其清除)? 如果没有、也许这是您真正要触发的 RIS 位? 我对这里的动态不是很清楚。]

因此、如果您的目标是 CK 的最短高电平周期(在限制范围内)、则 MEMRESIFG 似乎非常接近(或 STATUS:BUSY)。 我在 TRM 图 12-1 中看不到任何会将采样信号[图 12-2]带入外部的内容。 (面对来自其他渠道的竞争,DMA 不是确定性的,但我期望它足够快。)

在论坛上、我看到了一些提示、ADC 可能对在繁忙时触发很敏感、因此如果 CK 低电平周期与上面的示例一样短、那么出于这个原因、您可能需要等待完成 (BUSY==0)。

您是否仍计划使用 MISO(还是它是 MOSI)来执行 CK 触发器、而不是讨价还价 GPIO? 我问道、因为前者的占空比为 50%、但不需要 GPIO(或计时器)。

谢谢...明白了。 我现在有了以下内容:

我的代码中有错误、未使用 Vref 缓冲区...

然而,如果我现在这样做,它只是挂起,永远不存在循环??

第一个循环...

'是否有理由将 CCK 引脚(高电平)设置两次?'

这是星期一…

这适用于第一个 CCK

当您之前询问过这一点时、我做了一个实验(ADC12_max_freq_DMA 的有点黑客版本)、让我确信 DMA 清除 DMA_TRIG.RIS.MEMRESIFG0、而不是 CPU_INT.RIS.MEMRESIFG0。

MEMRES0 的 DMA 读取(在 TRM 表 12-20 中)本身显然不被计为“读取“、而是 DMA-ACK 来清除 RIS 位、而清除 CPU_INT.RIS.MEMRESIFG0 需要从 CPU 读取。 TRM 的第 12.2.14.1 节和第 12.2.14.3 节 暗示了这种区别、但前者没有明确提及 MEMRES 寄存器。

DL_ADC12_clearInterruptStatus () 指的是 CPU_INT。 DMA_TRIG 的相应调用是 DL_ADC12_clearDMATriggerStatus()。

您看到了不同的行为吗?

你好...是的、我认为、有点...

放置一个电阻器

> DL_GPIO_setPins (GPIO_SA3_CCK_PORT、GPIO_SA3_CCK_PIN);

插入

> DL_ADC12_clearInterruptStatus (ADC12_0_INST、ADC12_DMA_TRIG_RIS_MEMRESIFG0_MASK );//清除过时

由于 DMA 不执行此操作(这在本例中实际上是一项优势)、因此您必须执行此操作。

谢谢,但不应该 DMA 每次进行传输时都清除此内容?

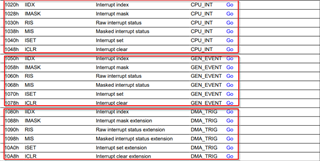

8.2.5.4 硬件事件处理

如果是源自 DMA 触发 (DMA_TRIG) 或通用事件 (GEN_EVENT) 的事件、则 IIDX

未使用寄存器。 在生成事件的外设之间执行四次事件握手

和订阅事件的硬件实体(例如,DMA 或辅助外设)。

四次事件握手将清除 RIS 和 MIS 寄存器中相应的中断状态位

自动化。

DL_ADC12_getRawInterruptStatus 的定义如下所示:

__STATIC_INLINE uint32_t DL_ADC12_getRawInterruptStatus(

const ADC12_Regs *adc12, uint32_t interruptMask)

{

return (adc12->ULLMEM.CPU_INT.RIS & interruptMask);

}

即、它仅查看 CPU_INT.RIS。 相比之下、您可以使用以下命令来获得 DMA_TRIG.RIS:

__STATIC_INLINE uint32_t DL_ADC12_getRawDMATriggerStatus(

const ADC12_Regs *adc12, uint32_t dmaMask)

{

return (adc12->ULLMEM.DMA_TRIG.RIS & ~(dmaMask));

}

[那“~“肯定看起来不对,是吗? 我想知道是否有人使用过此函数。]

实际上、每个外设中(多个)RIS 寄存器的 RIS 位定义相同(也是 IMASK/ICLR/等)、但命名不同(CMSIS 要求)、因此 (ADC12_DMA_TRIG_RIS_MEMRESIFG0_MASK == ADC12_CPU_INT_RIS_MEMRESIFG0_MASK );使用备用位名称不会引用不同的 RIS 寄存器。

[编辑:在上面我建议的代码中、我没有注意到你在使用 DMA_TRIG_RIS 定义--我只是复制了你的定义。 但它仍然有效。]

你(们)好、谢谢。

我想我必须以不同的方式做到这一点。

尽管你(出色)的努力,我只是不明白为什么我必须:

放置一个电阻器

> DL_GPIO_setPins (GPIO_SA3_CCK_PORT、GPIO_SA3_CCK_PIN);

插入

> DL_ADC12_clearInterruptStatus (ADC12_0_INST、ADC12_DMA_TRIG_RIS_MEMRESIFG0_MASK );//清除过时

由于 DMA 不执行此操作(这在本例中实际上是一项优势)、因此您必须执行此操作。

由于 TRM 提示 RIS 位在每个 DMA 后都会复位、所以为什么我需要清除它????

8.2.5.4 硬件事件处理

如果是源自 DMA 触发 (DMA_TRIG) 或通用事件 (GEN_EVENT) 的事件、则 IIDX

未使用寄存器。 在生成事件的外设之间执行四次事件握手

和订阅事件的硬件实体(例如,DMA 或辅助外设)。

四次事件握手将清除 RIS 和 MIS 寄存器中相应的中断状态位

自动化。

“每次 DMA 后 RIS 位会复位“。 关键是:哪个 RIS[:MEMRESIFG0]位? ADC 中有 3 个 RIS:MEMRESIFG0 位。 观察到的行为是 DMA 只清除其中 1 个、并且一个不是您要查看的。 (如果它清除了所有 3x,则发生的速度太快,您的循环无法看到它很高,并且您的代码的行为会有所不同。)

当您插入我上面建议的 DL_ADC12_clearInterruptStatus () 调用时、您看到了什么行为?

非邀约:您正在编写一次性实验、还是您打算以何种方式长期进行触发? 状态:BUSY 检查可能会在 99%的时间内工作[假设不是 0%]、因此可能足以进行实验。

尊敬的 Filip:

关于您关于 DMA 的问题、我想跳转 一下、添加一些注释。

M0 支持三种不同的事件系统、CPU_INT 用于 CPU 中断请求。

第二个是 GEN 事件、用于外设触发、如事件系统所用的 GPIO 触发 ADC。

最后一个是 DMA 事件、因此如果发生 DMA 传输、DMA 将由硬件清除该事件。

至于 ADC 转换状态监控器、通常 会轮询 CPU_INT RIS、然后应该清除 CPU_INT RIS、因为它不会被 DMA 清除。

B.R.

Sal

谢谢。

这似乎有效:

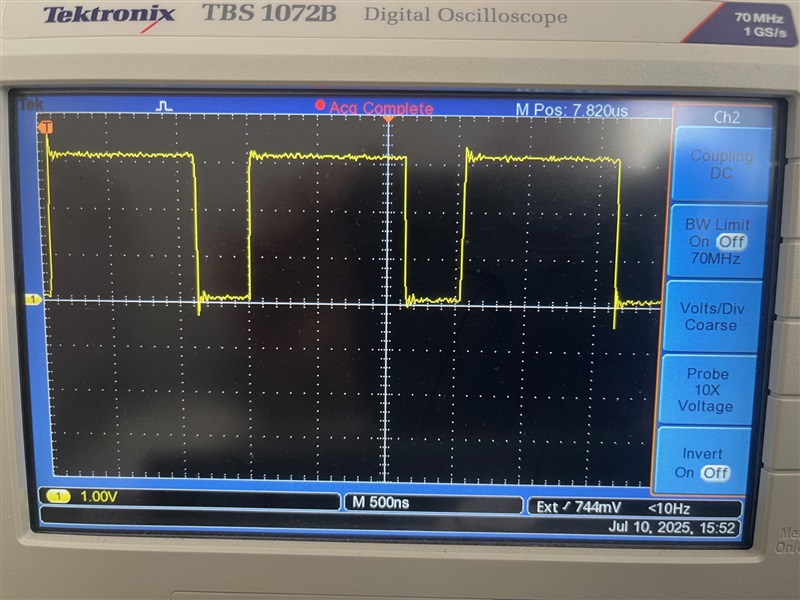

8.1.5 事件传播延迟

通用路由通道在发布实体和之间实现了四路硬件握手

订阅实体。 此握手需要四个 ULPCLK 周期才能完成:

(c) 当 ADCCLK 以 ULPCLK 为时钟源时、同步延迟 (tsync) 被旁路、并且采样信号使用 ADC 触发变为有效

ADC 8 位转换需要 9 个时钟周期、包括写入 memres0。

因此、我认为所需的一切:100ns + 300ns + 9*25ns = 625ns

然后把 CCK 低。。

似乎是一个巨大的差异。。。