主题:SysConfig 中讨论的其他器件

工具/软件:

您好:

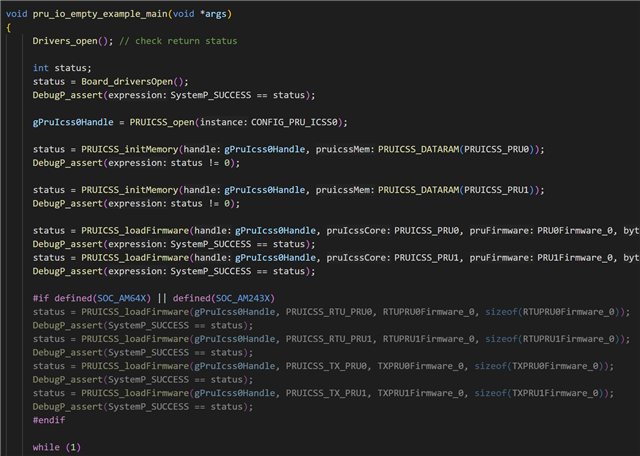

我对创建 GPIO 输入中断有几个问题。

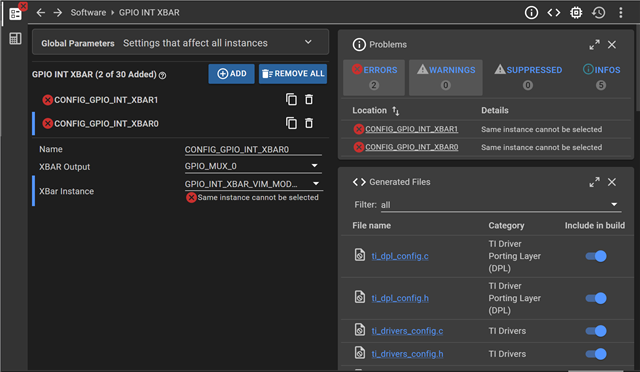

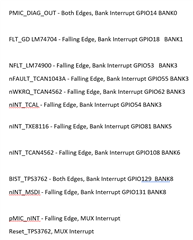

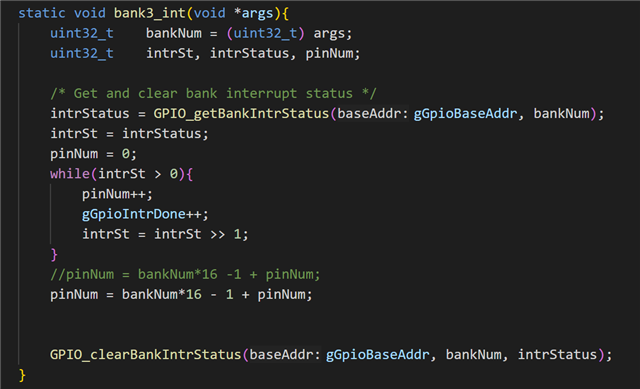

- 我尝试针对 12 个 GPIO 触发输入中断。 其中 2 个是多路复用器中断、而其他 10 个则分布在 6 个组之间。 因此、我需要 8 个中断条件实例。 多个实例是否可以使用相同的中断条件、因为我尝试这样做时遇到了错误。

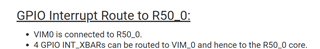

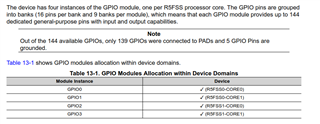

- 如果没有、一个内核是否只能处理四个中断条件(例如,对于内核 0、它将是 R5FSS0_CORE0_INTR_INTRXBAR_OUT_14 到 R5FSS0_CORE0_INTR_INTRXBAR_OUT_17、它们对应于 XBar 实例 GPIO_INT_XBAR_VIM_MODULE0_0 到 GPIO_LE0_VIM_DU3)? 或者是否有其他中断条件可供选择? 如果我有其他中断条件可供选择、它们对应的 xbar 实例是什么?

- XBar 实例的其他类型有哪些(例如 GPIO_INT_XBAR_ICSS_XBAR_0)

谢谢!

Saanvi