工具/软件:

您好支持团队、

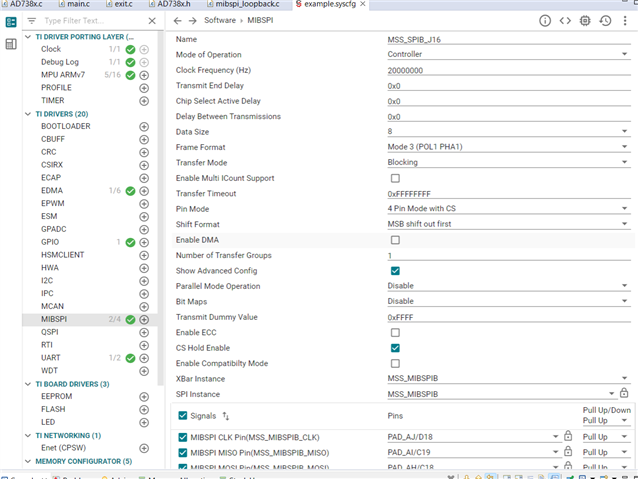

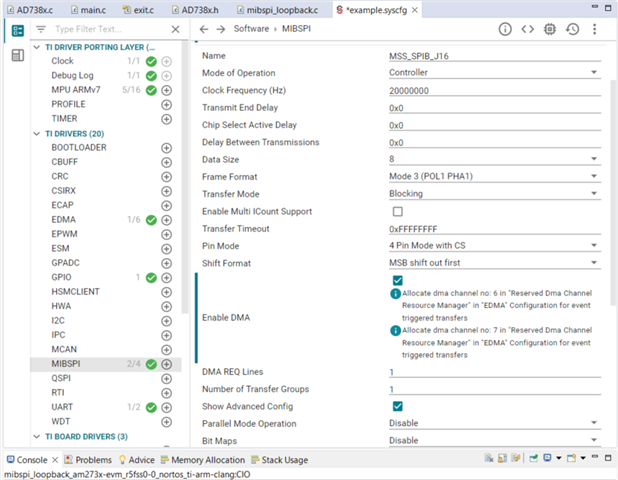

我们使用 AM273x 通过 SPI 从 AD7389-4 ADC 芯片组收集数据。 现在我们发现、输入数据的采样率受 AM273x 中 SPI 的 CS 速率的限制。 如下面的屏幕截图所示、SPI 时钟为 20MHz、4 引脚模式、启用 CS 保持功能时、CS 信号周期为 14.25us、因此我们得到的采样率为 70.2KHz

是否有办法提高 CS 速率? CS 速率的限制是多少?

我的数据收集源代码如附件所示。 如果我出了问题、您能查看一下吗? 还是我在每个 SPI 事务之间产生了任何额外的延迟?

e2e.ti.com/.../void-AD738x_5F00_dataConversion_2800_void_2900_.txt

另外、为了了解更多信息、我附上了一个 Saleae 捕获文件以供您参考。 (请将其从 xxx.txt 重命名为 xxx.Sal)

e2e.ti.com/.../Session10_5F00_latestOne.txt

非常感谢您的帮助和支持。

期待您的答复。

此致、

LIN