工具/软件:

尊敬的 TI 支持团队:

我正在使用 MSP432E4 MCU、并尝试在上生成 PWM 信号 PF1 (M0PWM1) 。 PF1 引脚连接到另一侧的 FPGA、其中 PWM 输出将用作基准时钟。

我已使用 PLL 和启用的 PWM0 将系统时钟配置到 120MHz。 PF1 引脚配置为GPIO_PF1_M0PWM1、我正在使用 PWM 发生器 0、输出 1 。 我的代码基于 TI 的 driverlib、并遵循了标准的初始化步骤:

-

系统时钟设置为 120MHz

-

SysCtlPeripheralEnable()GPIOF 和 PWM0 稳压器 -

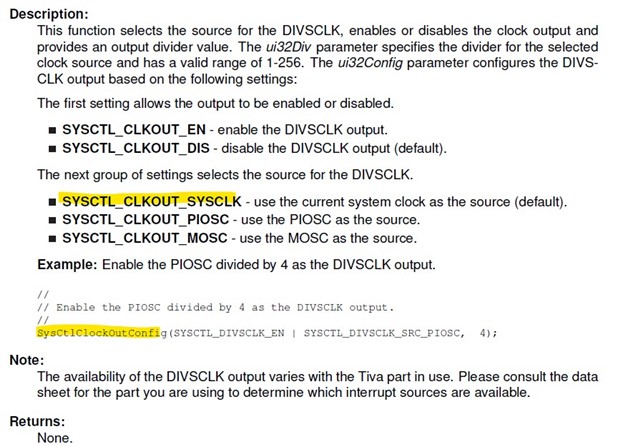

SysCtlPWMClockSet(SYSCTL_PWMDIV_1)以获得最大 PWM 分辨率 -

使用

GPIOPinConfigure(GPIO_PF1_M0PWM1)和配置 PF1GPIOPinTypePWM() -

PWMGenConfigure(PWM0_BASE, PWM_GEN_0, PWM_GEN_MODE_DOWN) -

PWMGenPeriodSet()PWMPulseWidthSet()用于配置周期和占空比 -

PWMOutputState()PWMGenEnable()可调用

但是、我观察到了这一点 PF1 始终保持高电平 或者、如果我更改任何内容、在 PF1 引脚中看不到任何输出。 即使我配置为低频(例如,1kHz、50%占空比)、也看不到预期的波形。

您能否澄清以下几点?

-

是否需要任何其他配置 M0PWM1 (PF1) 输出?

-

PF1 上可实现的最大 PWM 频率是否存在已知限制?

-

直接从 PWM 引脚驱动 FPGA 输入时、是否存在任何限制?

下面我提供了我的代码供您参考、

#include

#include

#include “ti/devices/msp432e4/driverlib/driverlib.h"</s>“

#define SYSTEM_CLOCK_HZ 120000000 // 120MHz 系统时钟

#define PWM_FREQUENCY 1000 // 1kHz 以方便观察

#define PWM_DUTY_PERCENT 50 // 50%占空比

uint32_t ui32SysClock;

uint32_t ui32Period;

// 1。 使用 PLL 为 120MHz 配置系统时钟

ui32SysClock = SysCtlClockFreqSet (

(SYSCTL_XTAL_25MHz |

SYSCTL_OSC_MAIN |

SysCtl_USE_PLL |

SYSCTL_CFG_VCO_480)、

SYSTEM_CLOCK_Hz);

// 2. 启用外设

SysCtlPeripheralEnable (SYSCTL_PERIPH_PWM0);

SysCtlPeripheralEnable (SysCtl_Periph_GPIOF);

while(!SysCtlPeripheralReady (SYSCTL_PERIPH_PWM0));

while(!SysCtlPeripheralReady (SYSCTL_PERIPH_GPIOF));

// 3. 将 PF1 配置为 M0PWM1

GPIOPinConfigure (GPIO_PF1_M0PWM1);

GPIOPinTypePWM (GPIO_PORTF_BASE、GPIO_PIN_1);

// 4. 在配置前禁用发生器

PWMGenDisable (PWM0_BASE、PWM_GEN_0);

//将生成器 0 配置为向下计数模式

PWMGenConfigure (PWM0_BASE、PWM_GEN_0、PWM_GEN_MODE_DOWN);

// 5. 设置 PWM 周期和占空比

ui32Period =(ui32SysClock/PWM_FREQUENCY);

PWMGenPeriodSet (PWM0_BASE、PWM_GEN_0、ui32Period);

//将占空比设置为 50%

PWMPulseWidthSet (PWM0_BASE、PWM_OUT_1、(ui32Period * PWM_Duty_Percent)/ 100);

// 6. 启用 PWM 输出

PWMOutputState (PWM0_BASE、PWM_OUT_1_BIT、TRUE);

//启用生成器

PWMGenEnable (PWM0_BASE、PWM_GEN_0);

while (1)

{

//永远循环–PWM 在硬件中运行

}

感谢您在解决此问题方面提供指导、因为 PF1 输出对于我的设计至关重要。

此致、

J.Manikandasamy