主题: SysConfig 中讨论的其他器件

工具/软件:

您好、

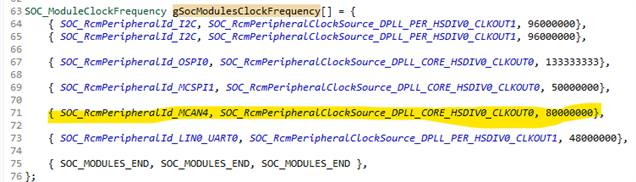

我有一个可正常工作的多核工程、在 devboot 模式下使用 CCS 加载时、工作正常。 MCAN 波特率应为 1000kbit/s

但是、当这个工程在 OSPI 引导模式下通过 SBL 从闪存加载时、波特率错误、约为 310kbit/s

- 这里的问题可能是什么?

- 使用 CCS 加载时、gel-files 会执行许多时钟配置。 通过 SBL 引导时、会在何处/何时发生这种情况? 我是否需要在 SBL 中进行一些额外的配置?

其他信息:

SoC:AM263P4_ZCZ_F

MCAN 代码主要来自“CAN_EXTERNAL_READ_WRITE_"示“示例

SBL 代码主要来自“sbl_ospi"示“示例

此致、

Frank