工具/软件:

您好:

我们集成了 MSPM0G3507-Q1 以进行定制设计。 我们添加了一个 24MHz 外部晶体(负载电容 8 pF ->我们在 XTAL 上使用 12 pF 电容)。 我们使用示波器验证了晶体及其在指定容差范围内。

我们得到了一些样本、并使用软件刷写了这些样本。 我们的软件会创建一个具有 5MHz 时钟的简单 PWM 计时器。 如果 PCB 变得更热、时钟变得更加不稳定(PLL 处于活动状态)、计时器时钟会在某个 kHz 左右波动、这不在容差范围内。

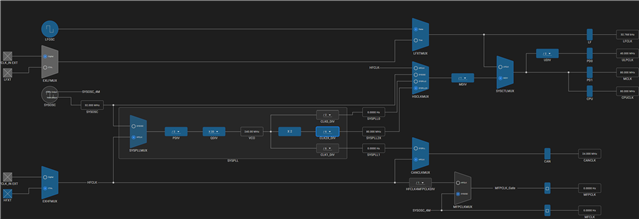

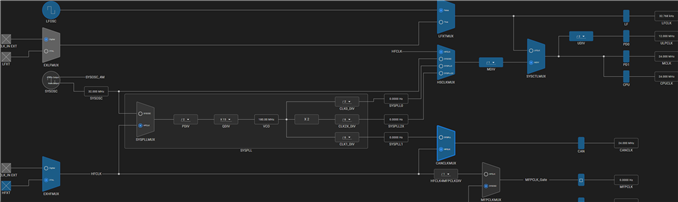

最初的时钟树配置

我进行了一些测试、使用了一个简单的示例 gpio_toggle_output 并修改了此示例。 我刚刚修改了时钟树并添加了一个带 5MHz 的 PWM 计时器、没有 GPIO 引脚正在切换。

目的是确定不稳定的根源,我做了 4 次尝试:

初次尝试:

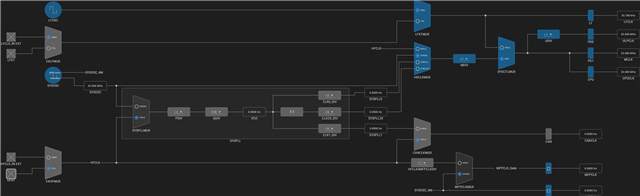

仅在该时钟树配置中使用内部时钟 SOSC

--> 4MHz 时钟输出稳定

第二次尝试:

仅在 PLL 有效的情况下使用内部时钟 SOSC

-->当 4MHz 处于激活状态时、PLL 时钟不稳定--> 这可能是由于 PLL 造成的

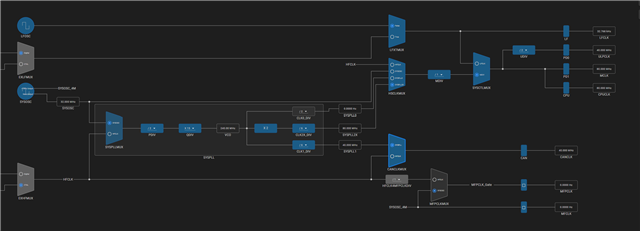

第三次尝试:

不带 PLL-> 4MHz 时钟输出稳定的外部 24MHz 晶体

第四次尝试:

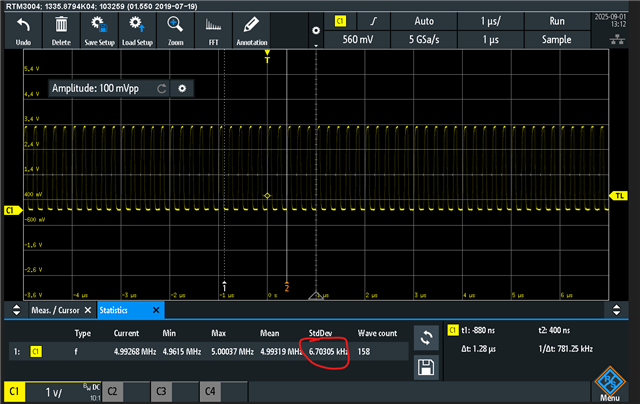

具有 PLL 的外部 24MHz 晶体(原始时钟树)-> 5MHz 时钟输出不稳定

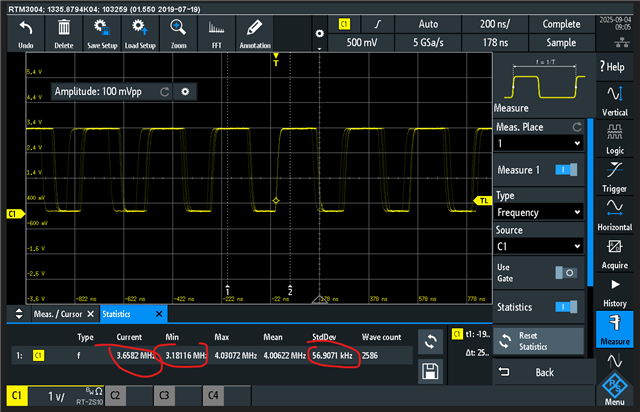

范围内的图片(标准偏差> 6kHz 增加至 30kHz)

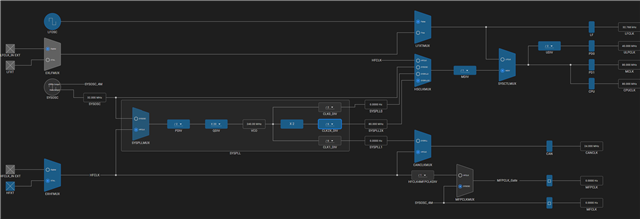

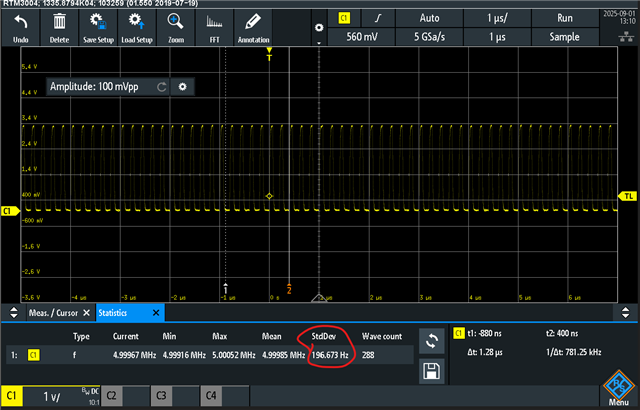

如果我将 clk2x_Div 从 6 放大到 8 --> CPU_CLK

60MHz 而不是 80MHz -->计时器的输出时钟 (5MHz) 也是稳定的!

示波器图片(标准偏差< 200Hz)

因此 PLL 配置似乎有问题。

在 SYSCTL“启用时钟稳定检查“中始终开启。 我们使用 CCS 20.0、但使用哪个版本无关紧要。 我们还有一些样片、这些样片的 80MHz 输出 PLL 配置没有问题。

我们不确定我们的某些 MCU 是否存在温度问题、则焊接问题不可见。 有时我们会更改 IC、然后使用原始配置。 PLL CONFIG、CLOCK CONFIG 或 TIMER CONFIG 是否存在任何已知问题、这些问题可能会导致温度升高而导致不稳定的时钟(任何预分频设置或其他设置)?