器件型号: AM2612-Q1

尊敬的专家:

美好的一天! 我要找客户。

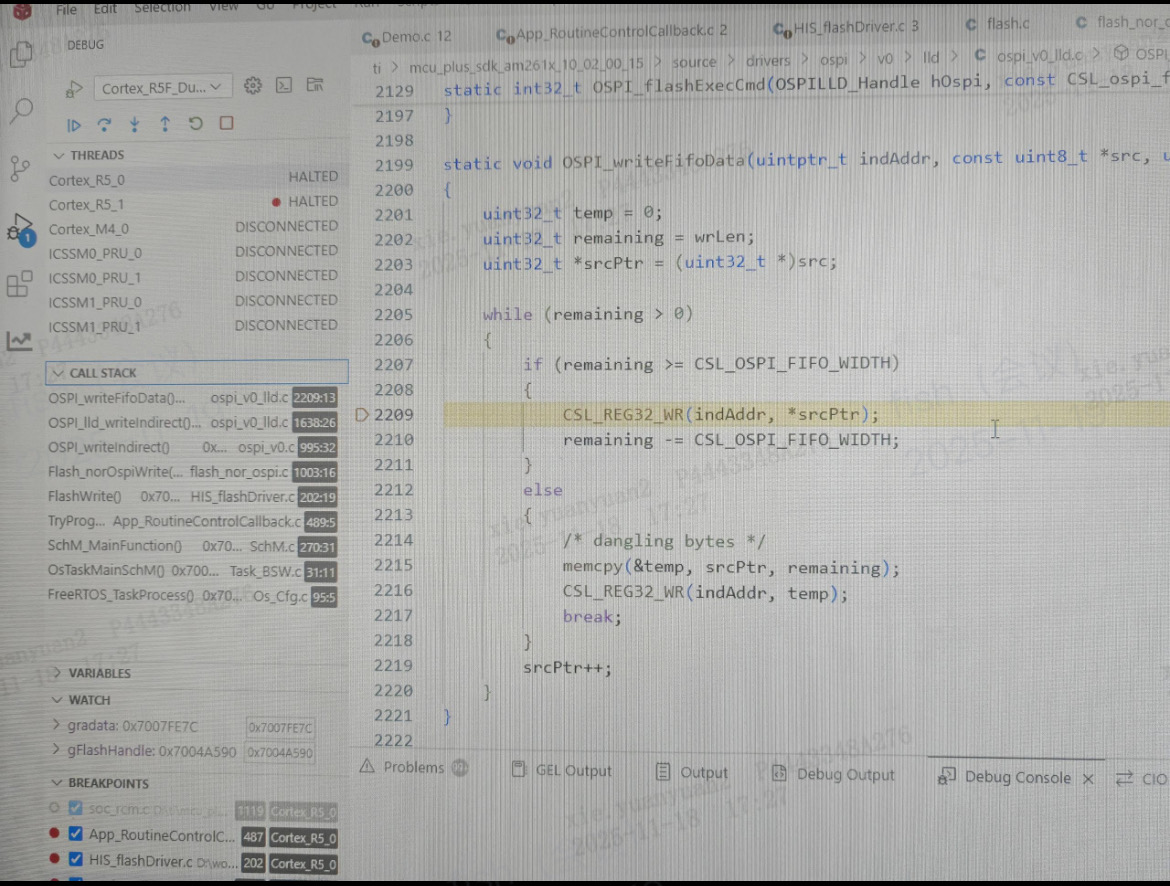

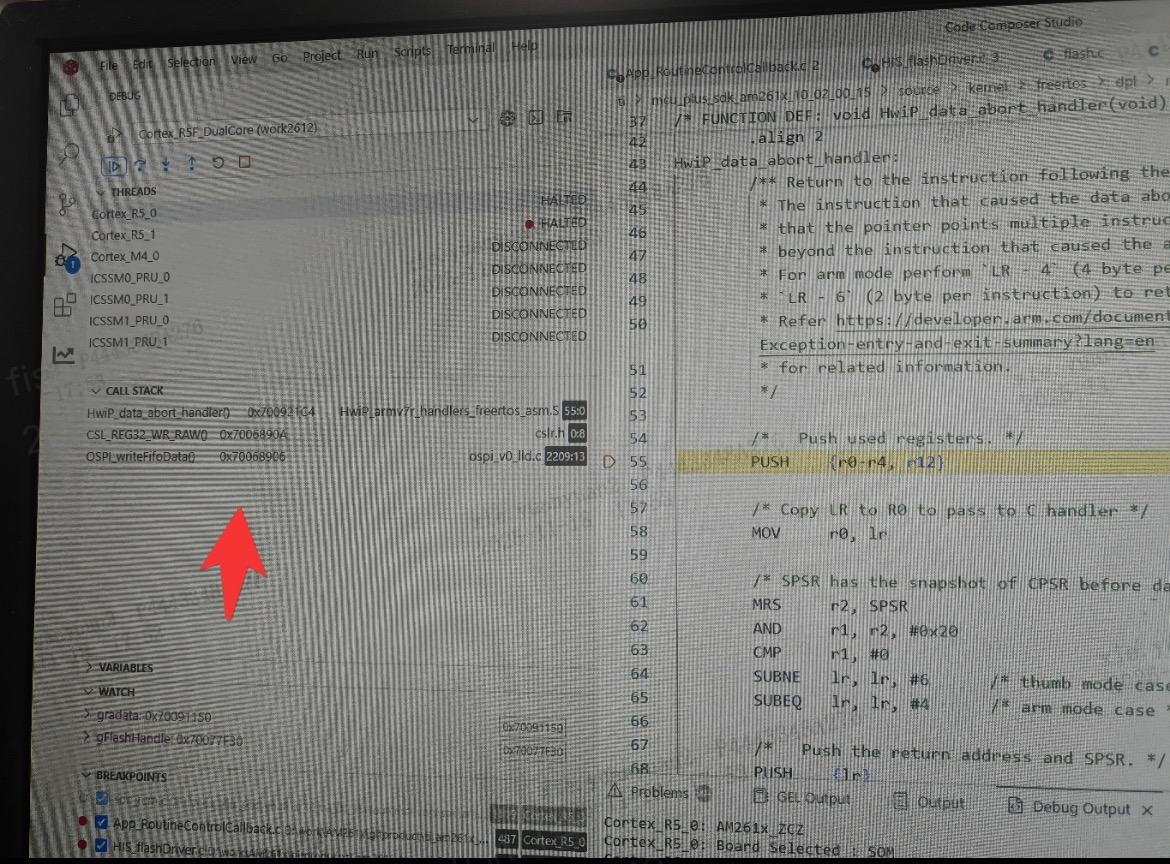

我的客户使用自己的电路板开发 AM261。 他们将调用函数函数 OSPI_writeFifoData () int 他们的代码。 他们在使用构建配置构建代码时发现了这一点 “调试“ 、它可以在调试代码时很好地运行闪存。 但在他们使用构建配置构建代码时 “释放“ 、CPU 将跳至 Hwip_data_abort_handler 。

在跳转到 Hwip_data_abort_handler 之前、它在 CSL_REG32_WR (indAddr、*srcPtr) 上运行。 此问题将发生在地址 0x880000 上、长度为 256 字节。

您能帮助检查导致 CPU 跳转到什么位置吗 Hwip_data_abort_handler 当执行 OSPI_writeFifoData () 时? 函数 OSPI_writeFifoData () 上的“release"和“和“debug"之间“之间有何区别

此致

Kita