Other Parts Discussed in Thread: AM263P4, SYSCONFIG

器件型号: AM263P4

主题: SysConfig 中讨论的其他器件

工具/软件:

问题 1:

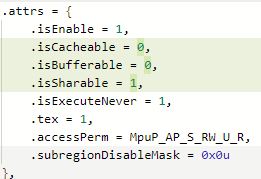

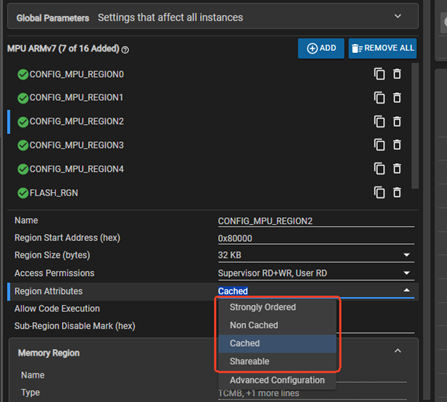

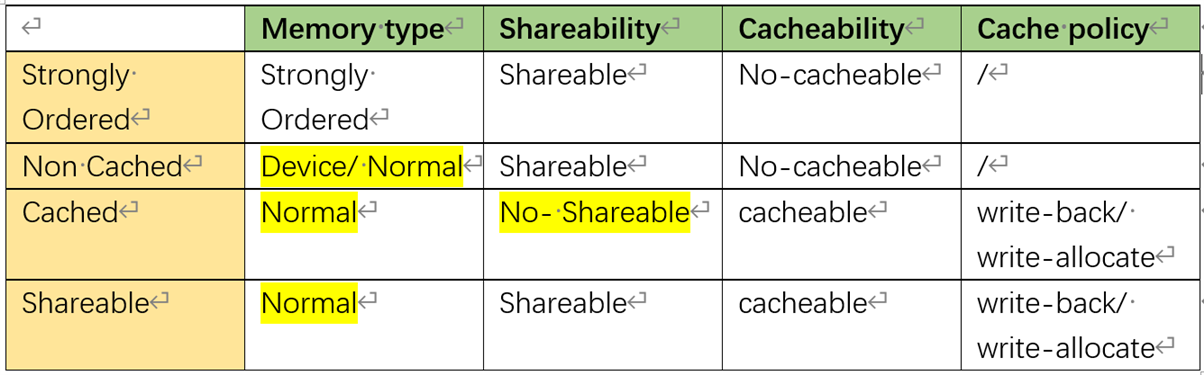

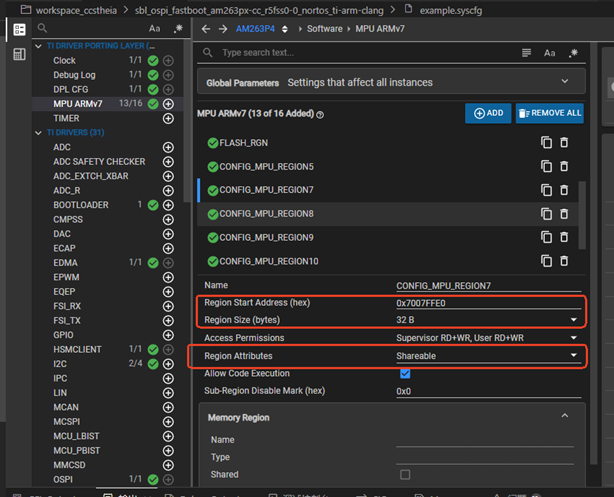

在 AM263P4 的 syscfg 配置中、区域属性配置是否仅限制为某些组合、而不是存储器类型、可共享性、可缓存性和高速缓存策略的所有可能组合?

我想确认我对 syscfg 中提供的“区域属性“组合的理解是否正确、尤其是突出显示的条目。?

问题 2:

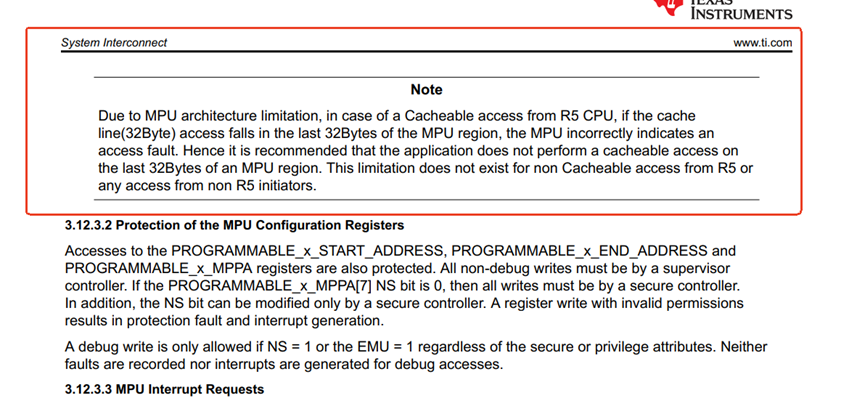

根据 TRM 手册、每个 512KB 的最后 32 个字节必须配置为非缓存。 但是、在 fastboot 示例中、该区域设置为可共享。 与缓存+可共享等效不可共享?

问题 3:

在快速引导示例中、RAM 配置为缓存。 执行相关的闪存操作后、使用 CacheP_WB 实现高速缓存和 RAM 之间的数据一致性以同步数据。 在非快速引导 SBL(次级引导加载程序)中、RAM 区域配置为可共享。 鉴于可共享暗示缓存、这是否还需要使用 CacheP_WB 在缓存和 RAM 之间同步数据以确保一致性?

如果一个区域配置为可共享、则它允许多个处理内核共享数据、而缓存的处理内核则不共享数据。 这是否就是将 RAM 区域配置为缓存会阻止 R5 内核访问 OTP 数据的原因? 但是、这就引出了另一个问题:在快速启动示例中、RAM 设置为缓存、那么从闪存读取 HSM 固件如何也可以与 HSM 内核共享?

问题 4:

AM263P4 目前是否仅支持写回和写分配高速缓存策略? 因此、每当 RAM 区域配置为缓存时、只能通过回写来保持数据一致性。 这是否意味着自动数据一致性理论上只能通过直写实现? 如何确定缓存将处理哪些数据、即何时执行手动数据同步(回写)?