Other Parts Discussed in Thread: TMDS273EVM

器件型号: TMDS273EVM

大家好、TI 大师们、

使用 TMDS273EVM 的 Im、我的目标是通过发送一些缓冲器并使用示波器监控信号来评估 LVDS 接口。

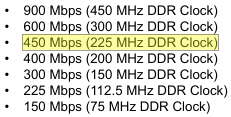

使用默认示例时、通过测量 225MHz CLK_P 并将其与 TRM 中支持的值 (SPRUIU0E) 对齐、我看到选择了 2 个通道、配置为 450Mbps(LVDS DDR 时钟):

示例驱动程序配置 HSI 时钟:

/* Configure HSI interface Clock */

HW_WR_REG32(CSL_MSS_TOPRCM_U_BASE + CSL_MSS_TOPRCM_HSI_CLK_SRC_SEL, 0x222);

HW_WR_REG32(CSL_MSS_TOPRCM_U_BASE + CSL_MSS_TOPRCM_HSI_DIV_VAL, 0x333);

为了使用其他支持的模式和数据速率、我需要您的帮助来解释这一点:

通过浏览 TRM 和时钟架构、我看到它利用了 时钟源:PLL_DSP_CLK (0x222 -> 2 ):

时钟分频器为 0x333->3:

- 我 在此表中看不到分频器值 3 “我在担心什么?“

- 225MHz 时钟是如何生成的 使用这些设置(来源:2、分频器:3)?

- 我希望按顺序发送多个缓冲区 、但当我在循环中激活/停用会话时、代码不会按预期运行(仅当我再次运行此示例时)、那么此驱动程序处理连续数据流的最佳做法是什么?

提前感谢、

Konstantinos