Other Parts Discussed in Thread: TMS570LC4357, HALCOGEN

器件型号: TMS570LC4357-TMS570LC4357 EP

Thread 中讨论的其他器件: TMS570LC4357、 HALCOGEN

尊敬的 TI 团队

通过 DMA 读取数据并将其写入存储器缓冲区时、我遇到了以下情况:

在调试执行期间、数据在缓冲区中可见、但暂停的数据显示为零。

我最终找到了我引用的论坛帖子、但仍然无法确定如何将缓存类型更改为直接写入模式。 后来,我禁用了缓存,发现数据存在于缓冲区中。

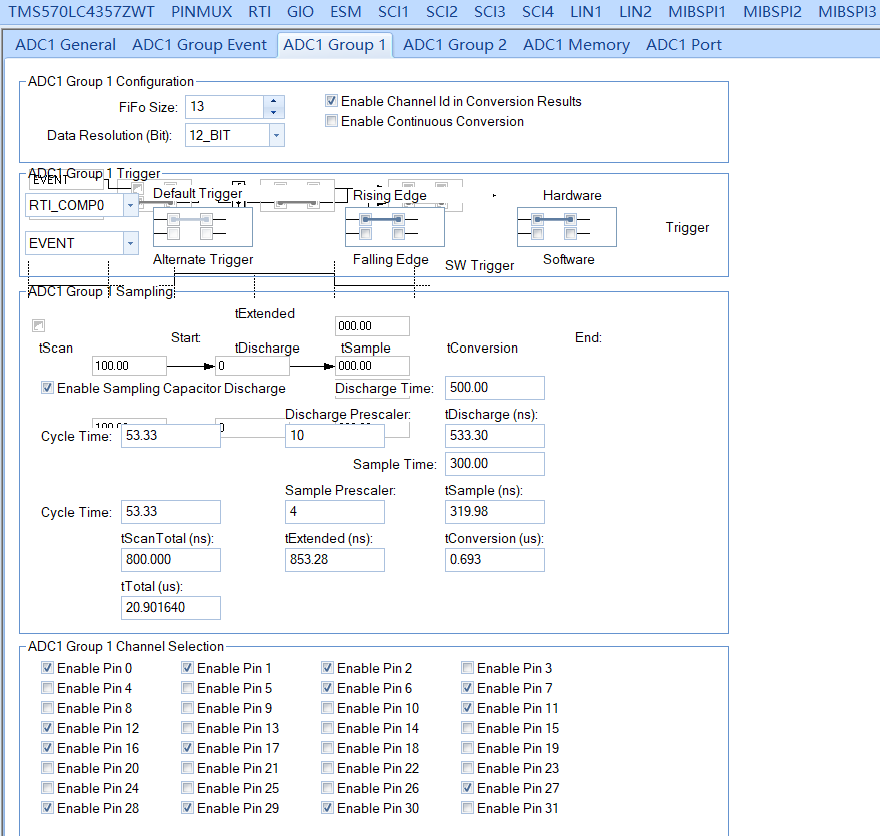

配置如下:

1.如何将缓存类型更改为直写? 更改后是否会有任何不利影响?

2. ADC 连续转换模式+组存储器阈值中断或周期性触发源 (RTI/ePWM)+DMA 的常见用法是什么?

3、是否需要使用 DMA 收集 10 次数据并对每个通道的数据求平均值?(在单个会话中收集的数据是否足够准确?)

4. MibADC1 中是否只有三个阈值中断? (每个通道的阈值中断不可能?μ s)

最后是我的代码,期待着答复,谢谢。