“线程:HALCOGEN, 测试”中讨论的其它部件

大家好,

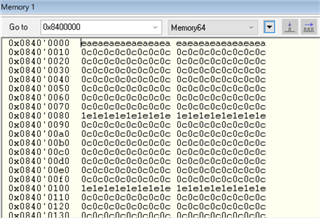

在我们的项目中,启用了 ECC 以检测 SRAM 双位错误。 我们正在寻找一种模拟双位奇偶校验错误并查看其影响的方法。

但是,阅读完 TCRAM 模块的 SPNU499c 第6.6段仿真/调试模式行为后,调试器似乎无法在调试模式下强制执行此错误。

在检测到错误时,确保正确启用 SRAM ECC 并确认其影响的技术(如断言 nError pin)必须与 SECDEC 闪存错误检测和校正控制寄存器1的情况相同, 通过读取位于 OTP 的预定义地址?

非常感谢!