“线程:测试”中讨论的其它部件

您好,

这是一个有关 DMA 模块和 ESM1.88的高完整性位的问题。

我们已经检查了 SPNU563A 的 DMA 模块部分,但没有详细描述高完整性位。

我们希望识别 DMA 模块的高完整性位。

例如,SYS 模块被描述为 SPNU563A 第2.5.1.13节的以下内容。

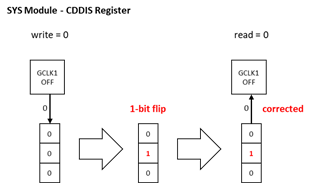

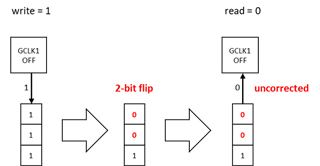

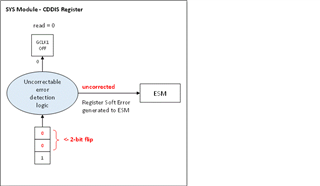

2.5.1.13时钟域禁用寄存器(CDDIS)

注:所有时钟域都在唤醒时启用。

应用程序应确保当通过 HCLKOFF 位关闭 HCLK 和 VCLK_sys 时,GCLK1域也会关闭。

CDDIS 中的寄存器位被指定为高完整性位,并通过纠错逻辑实现,因此每个位(尽管读写为单个位)实际上是具有纠错功能的多位密钥。 因此,可以纠正“密钥”中的单位翻转,以保护整个系统。 检测到的错误会发送给 ESM 模块。

请告诉我哪一个寄存器对应于高完整性位。

谢谢,

肖