主题:AM2434, sysconfig中讨论的其它部件

您好,

我们正在使用组装了AM2434和LPDDR4的定制板。

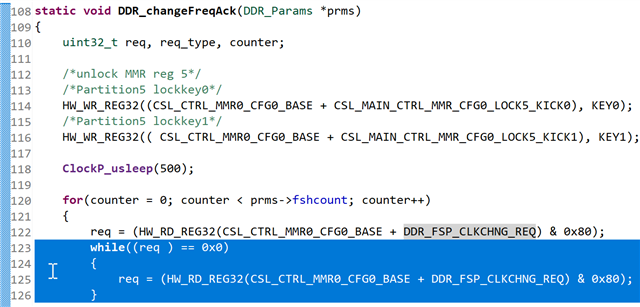

在LPDDR4的初始化过程中,我在DDR_changeFreqAck()中的第123行遇到死循环 请参阅下图。

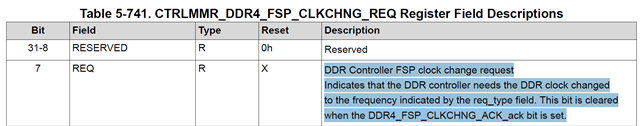

循环一直等待,直到CTRLMMR_DDR4_FSP_CLKCHNG_REQ寄存器的位7不为零。 它仅通过DDR4_FSP_CLKCHNG_ACK寄存器获得Cleard

CTRLMMR_DDR4_FSP_CLKCHNG_REQ的第7位在初始化过程中设置在哪里?

从DDR_setFreq()我没有收到错误消息。

祝你好

Tom