尊敬的香榭丽舍

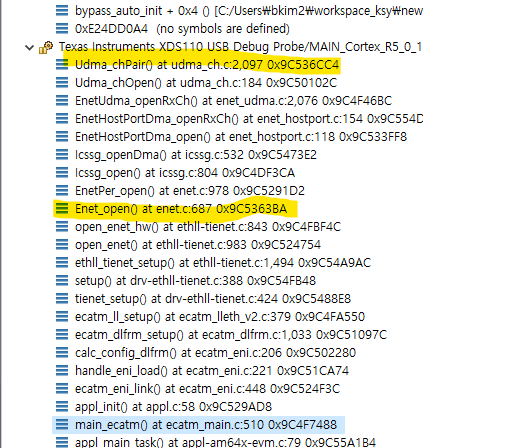

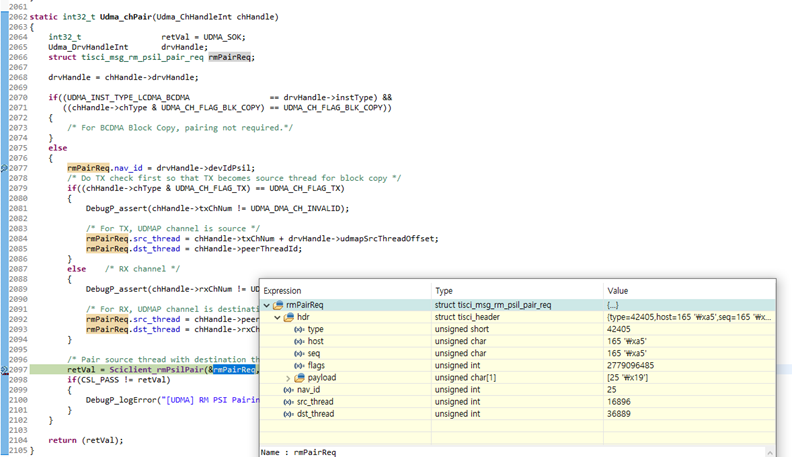

我的客户通过返回'-1'失败了 enet_open(),他们发现在 UDMA_chPair()函数的 sciclient_service 中没有设置'sciResp.flags & TISCI_MSG_FLAG_ACK Flag',并返回'-1',如下所示。

您能否查看下面的调用堆栈并让我知道应该进一步检查哪些内容?

他们的 MCU+ SDK 版本有点复杂。 它们使用 SDKv8.3.0中的 SBL、但应用是在 MCU+ SDK v8.2.0上开发的。

您是否认为 SBL 和应用程序之间的版本不匹配会导致此问题?

谢谢、此致、

SI