您好!

我所面临的情况是、启用 FIQ 仅在上电复位期间导致预取中止。

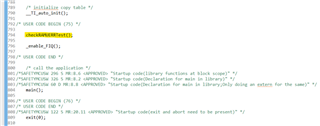

刷写软件后断开目标、然后执行上电复位、 系统未按预期运行、无法调试我连接到目标并发现系统 卡在 预取处理程序中的问题。

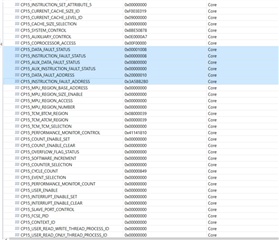

指令故障状态寄存器= 0x00000008

指令故障地址寄存器= 0x3E5BB2B0

SPSR_ABT 表示系统处于 FIQ 模式。 只有 ESM 中断为 FIQ、所有其它中断被配置为 IRQ

系统 在调试模式下按预期运行、但在上电复位后未运行、如果未启用 FIQ、我不会遇到此问题

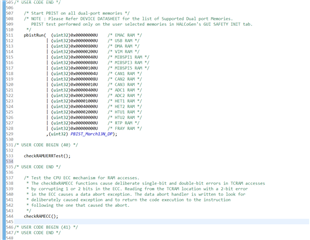

为了 解决这个问题、我在 预取中止处理程序中执行了 S/W 复位、并且在软件复位后、系统按预期运行、但我真的不理解这背后的根本原因。 如果我能在解决这个问题方面提供一些帮助、那将会非常好。

谢谢。