主题中讨论的其他器件: HALCOGEN

我想将 SCI 设置为在传输时使用 DMA、在不占用 CPU 的情况下打印数据。 在230400波特时,字符输出需要42微秒,因此如果 CPU 轮询,打印25个字符需要1毫秒,就像 sciSend()一样。

下面讨论了接收时的 DMA、但我无法判断结果是什么...

感谢所有帮助。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我想将 SCI 设置为在传输时使用 DMA、在不占用 CPU 的情况下打印数据。 在230400波特时,字符输出需要42微秒,因此如果 CPU 轮询,打印25个字符需要1毫秒,就像 sciSend()一样。

下面讨论了接收时的 DMA、但我无法判断结果是什么...

感谢所有帮助。

当成功接收到一个帧并且 DMA 功能已经被启用时、接收器 DMA 请求被置位。 当 SCI 将新接收到的数据从 SCIRXSHF 寄存器传输到 SCIRD 缓冲区时、RXRDY 标志被置位。 因此、RXRDY 标志指示 SCI 有新的数据要读取。 接收 DMA 请求由设置 RX INT 位启用。

/*启用 SCI3接收 DMA 请求*/

sciREG3->SETINT |= SCI_SET_RX_DMA | SCI_SET_RX_DMA_ALL | SCI_RX_INT;

我看不到 SCI_SET_TX_DMA 已定义、但芯片规格显示位16、因此我有以下代码:

sciInit();

/*启用 SCI3发送和 SCI3发送 DMA 请求*/

#define SCI_SET_TX_DMA (1 << 16)

printf ("SCI_TX_INT=0x%x\n"、SCI_TX_INT);

sciREG3->SETINT |= SCI_SET_TX_DMA | SCI_TX_INT;

printf ("sciREG3->SETINT=0x%x\n"、sciREG3->SETINT);

输出显示 SETINT 为0x0、而不 是至少为0x10100、这似乎表示某处关闭。

SCI_TX_INT=0x100

sciREG3->SETINT=0x0

这是一个长字符串、用于纯食食时间

uDIFF=2462.670

通过 sciSend 的显示保持在2.4毫秒(230400波特)、与轮询输出相同。

我假设 REG3是用于 sciSend()的控制台通道。

是否有一些测试项目可以证明这一点?

谢谢。

尊敬的 Peter:

[引用 userid="521569" URL"~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1103898/tms570lc4357-sci-transmit and 也许-receive-using-using-dma/4090531#4090531"]输出显示 的内容至少为0x100、而不是 SET/INT[.0X100]。在配置 SCI 寄存器之前、必须将 SCIGCR0寄存器的 RESET 位设置为1、并将 SCIGCR1寄存器的 SWnRST 位清零

[引用 userid="521569" URL"~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1103898/tms570lc4357-sci-transmit and 也许-receive-using-using-dma/4090531#4090531"]通过 sci/secabaud 以2.4 mbaud 的方式进行显示(以2.4 msci 的方式),与以2.4 mbaud/240秒的方式保持相同的输出(引用)。1个字符的传输时间为:(8位+ 2个停止位)/230400 = 0.0434ms。 在中断模式下传输字符不会比使用轮询模式节省您的时间。

我添加了以下 GCRx 写入、串行端口不再输出任何内容。 我必须做其他事情。

sciInit();

/*启用 SCI3发送和 SCI3发送 DMA 请求*/

#define RESET (1 << 0)

#define SWnRST (1 << 7)

sciREG1->GCR0 |=复位;

sciREG1->GCR1 &=~SWnRST;

#define SCI_SET_TX_DMA (1 << 16)

printf ("SCI_TX_INT=0x%x\n"、SCI_TX_INT);

sciREG3->SETINT |= SCI_SET_TX_DMA | SCI_TX_INT;

uint32 setint = sciREG3->SETINT;

printf ("sciREG3->SETINT=0x%x\n"、setint);

我没有显示执行打印时序的代码(使用轮询或 DMA)、但它是...

Timer_delay (1);//让前一个输出完全漏极

uint64 c_start = timer_cread ();

printf ("这是一个长字符串、纯粹用于占用时间\n");

uint64 c_end = timer_cread ();

float udiff = timer_udiff (c_start、c_end);

Timer_delay (1);//让输出完全漏极

printf ("udiff=%1.3f\n"、udiff);

产生了...

这是一个长字符串、用于纯食食时间

uDIFF=2462.390

使用 DMA 会产生一个不同的世界、因为它不是将 CPU 绑定2.4ms、而是以自己的方式执行其他(重要)任务。 对于 DMA、udiff 应显示远低于几微秒。

使用 DMA (或中断 IO)是系统(OS)在不浪费 CPU 时间的情况下为低速设备提供服务的常规方式。 sciSend()的实现实际上非常有限,因为它要求"用户"在每一个输出行(基本上是对 sciSend()的每次调用)上提供硬件的婴儿看护。 我将实现一个 write()层[类似于 Unix/Linux 系统调用],该层将用户发送的数据复制到系统缓冲区中(例如1KB),DMA 将从该缓冲区中吸出数据(使用重复 sciSend())。 因此、在超过1KB 缓冲区之前、用户"应用"不会被阻止。 或者、如果晚打印信息对显示不重要、(在不同模式下)用户输出可能会被尾拖(应用程序不会阻止)。

当然、我需要首先使 DMA 模式运行。

感谢所有帮助。

您好!

printf 函数是用于输出文本的标准 C 函数。 它将文本输出到 CCS 控制台、而不是 UART COM 端口。 printf 不使用任何 SCI 函数(sciSent()或 sciReceive())。

使用 DMA 可以 减轻 CPU 复制大型数据块的负担、因此 在 DMA 在存储器和 SCI 寄存器之间传输数据时、CPU 可以执行其他操作。 正如我之前的帖子中提到的、 当数据被写入 SCITD 且 TXRDY 被置位(对于 SCI TX)时、将生成 DMA 请求、当 SCI 将新接收到的数据从 SCIRXSHF 寄存器传输到 SCIRD 缓冲器时、将生成 DMA 请求。 SCI 花费的时间主要取决于 SCI 波特率。

下面是使用 DMA + SCI 的示例:

TMS570LC4357上的 SCI/LIN 模块支持 多缓冲接收器和发送器。 SCI/LIN 模块有8个独立的接收和发送缓冲器。 通过设置 Mbuf 模式位来启用多缓冲模式。 上面的示例也支持多缓冲模式。

您好!

我使用的是 printf()的常用嵌入式版本,而不是 CCS 提供的任何版本。 我目前已将低端连接到 sciSend (sciREG1、...)、但也可以轻松地使用另一个 sciREG 进行输出。 Halcogen 在 XL2-570LC43上显示了使用 SCI1的控制台。

我能够为 XL2-570LC43构建上述示例软件包、但(当然)无法运行、因为软件包源用于另一个电路板。

我将适当的代码段从 sys_main.c 复制到 hl_sys_main.c (对于 XL2-570LC43)、并得到以下错误:

source/subdir_rules.mk:9:目标'source/hL_sys_main.obj'的配方失败

"./SOURCE /HL_SYS_MAIN.c"、第183行:错误#20:标识符"scilinREG"未定义

"./SOURCE /HL_SYS_MAIN.c"、第434行:警告#112-D:语句无法访问

"./SOURCE/HL_SYS_main.c"、第450行:警告#179-D:变量"cSCI_printfbuffer"已声明、但从未引用

"./source/hl_sys_main.c"、第451行:警告#179-D:变量"length"已声明、但从未引用

"./SOURCE /HL_SYS_MAIN.c"、第483行:错误#20:标识符"scilinREG"未定义

"./source/hL_sys_main.c"、第486行:错误#167:函数调用中的参数太少

"./source/hL_sys_main.c"、第491行:警告#190-D:与其他类型混合的枚举类型

"./SOURCE /HL_SYS_MAIN.c"、第527行:错误#20:标识符"dmaBTCAInterrupt"未定义

"./SOURCE /HL_SYS_MAIN.c"、第560行:错误#20:标识符"scilinREG"未定义

"./SOURCE /HL_SYS_MAIN.c"、第567行:错误#20:标识符"linREG"未定义

"./SOURCE /HL_SYS_MAIN.c"、第597行:错误#20:标识符"scilinREG"未定义

"./SOURCE /HL_SYS_MAIN.c"、第610行:错误#20:标识符"scilinREG"未定义

"../SOURCE /HL_SYS_MAIN.c"、第627行:错误#20:标识符"scilinREG"未定义

9在编译"./source/hL_sys_main.c"时检测到错误。

因此、我用 sciREG1替代 scilinREG。

代码有一条注释、表示不支持 sciREG1 (由 DMA 硬件或软件?????)。

现在,两个错误是 dmaEnableInterrupt(),它需要 dmaIntGroup_t 参数(第167行)和未定义的 dmaBTCAInterrupt (第527行)。

如何解决这些问题?

非常感谢您的帮助。

我已经尽可能修改了代码,但是第一次调用 scidmaSend()似乎没有做任何事情,因为 DMA 中断 ISR 不会发生。 我将发送到控制台端口 sciREG1、初始的非 DMA 输出正常。 我浏览了 scidmaSend()代码,正在配置的寄存器看起来是合理的。 我有点盲目地被称为 dmaReqAssign(),所以 DMA_CH0被连接到引脚31 (sciREG1??);不知道这是不是正确的。

我是否可以上传 hL_sys_main.c、以便您查看并使用调试器浏览代码? 非常感谢。

/*分配 DMA 请求:带有请求线的通道0 - 1 - TX*/

/* DMA 请求29用于 LIN (SCI2)发送*/

/*请参阅数据表-默认 DMA 请求映射部分*/

// dmaReqAssign (DMA_CH0、29);

dmaReqAssign (DMA_CH0、31);// sciREG1 (见下文)

该示例不支持 sciREG1。 所有 SCI 模块都支持 DMA。

现在,两个错误是 dmaEnableInterrupt(),它需要 dmaIntGroup_t 参数(第167行)和未定义的 dmaBTCAInterrupt (第527行)。

如何解决这些问题?

[/报价]dmaEnableInterrupt (uint32通道、dmaInterrupt_t inttype) -->用于 tms570lsx 器件

dmaEnableInterrupt (dmaChannel_t channel、dmaInterrupt_t inttype、dmaIntGroup_t group) ->由 TMS570LC43x 和 RM57器件使用。

示例:

dmaEnableInterrupt (DMA_CH0、BTC、DMA_INTA);

不、不正确

以下 DMA 请求行被分配给 SCI:

SCI1_TX DMA_REQ29

SCI1_RX DMA_REQ28

SCI2_TX DMA_REQ40

SCI2_RX DMA_REQ41

SCI3_TX DMA_REQ31

SCI3_RX DMA_REQ30

SCI4_TX DMA_REQ43

SCI4_RX DMA_REQ42

如果您使用 SCI1 (或 LIN1/SCI1)、则 DMA 请求线对于 TX 为29、对于 RX 为28:

dmaReqAssign (DMA_CH0、29); //SCI1 RX

dmaReqAssign (DMA_CH1、28); //SCI1 TX

相关代码部分如下所示。 此后、我对使用 sciREG1进行了一些小的编辑。 在任何情况下,"NOTUSED"部分都是原始代码,声称31是 sciREG1的代码。 在单步执行代码时、我尝试查看了《技术参考手册》、该手册似乎认为31是正确的值。 映射位令人困惑、但似乎说在正确位置(位24至29)的一些位堆映射到特定的 DMA 通道(0)。

我刚刚尝试了29个值(大概是 sciREG1 TX),scidmaSend()仍然像以前一样挂起。

请注意,当使用31值时,我看到 dmaBTCAInterrupt 上有一个断点正在触发_Befor_到达 scidmaSend(),因此31将某些内容路由到该中断。 不幸的是,调用 scidmaSend()后,该中断不会发生。

/*接收数据后启用中断*/

dmaEnableInterrupt (DMA_CH0、BTC、DMA_INTA);/* DMA_CH0为最高优先级*/

/*分配 DMA 请求:带有请求线的通道0 - 1 - TX*/

/* DMA 请求29用于 LIN (SCI2)发送*/

/*请参阅数据表-默认 DMA 请求映射部分*/

// dmaReqAssign (DMA_CH0、29);

dmaReqAssign (DMA_CH0、31);// sciREG1 (见下文)

}

#ifdef NOTUSED

否则、如果(sci =sciREG1){

return;/*目前不支持 SCI1 */

/*接收数据后启用中断*/

/* dmaEnableInterrupt (DMA_CH1、BTC);// dma_CH0是最高优先级*/

/*分配 DMA 请求:带有请求线的通道0 - 1 - TX*/

/* DMA 请求31用于 SCI1发送*/

/*请参阅数据表-默认 DMA 请求映射部分*/

/*dmaReqAssign (DMA_CH1、31);*/

}

#endif // NOTUSED

否则{

返回;//未知寄存器*/

}

BTCA 中断是由于调用_enable_IRQ()后使用 sciSend ()的 sci_printf()调用引起的。 我使用的是31还是29。 原始代码旨在在测试 linREG1 (scilinREG)时使用 sciREG1来显示测试状态、因此没关系。 我在 scidmaInit()之前移动了 sci_printf(),以缓解问题。 我的印象是即使在调用 scidmaInit()和_enable_irq()之后,sciSend()也可以使用,但这可能不正确。

我希望29或31现在可以工作,但事实并非如此,scidmaSend()之后的行为保持不变。 就好像 scidmaSend()在实际启动 DMA 时有一些问题,因为显示字符串不会出现(与之前 sci_printf()/sciSend()向外发送字符串(并导致 BTCA 中断)的情况不同)。 我单步执行 scidmaSend()代码,它看起来很好;我真的看不到可以在它中进行任何更改来解决问题。

谢谢。

sci_printf ("scidmaSend 示例-用于将单字节从 RAM 传输到 SCI\n"\});

/*用于 DMA 传输的 Init serREG */

scidmaInit (serREG);/*要求首先调用 sciInit */

/*启用 CPU 中断*/

_enable_IRQ ();

// sci_printf ("scidmaSend 示例-用于将单字节从 RAM 传输到 SCI\n\r\n"DMA);

scidmaSend (buffer);

/*在此处输入代码,但不要再次调用 scidmaSend */

/*等待 DMA 中断 ISR 设置标志*/

while (DMA_Comp_Flag!= 0x55AAD09E){

IDLECOUNT++;

}

/* scidmaSend 已完成,可以再次调用*/

sci_printf ("\n\n\r\n\r\n\r\n");

我本以为 scidmaSend()中的最后几行已经启动了 DMA 并显示了测试字符串(其中 serREG == sciREG1)。 但是、我在终端上看不到任何东西。

/*-设置用于传输的 DMA 控制数据包*/

dmaSetCtrlPacket (DMA_CH0、g_dmaCTRLPKT);

/*-将 DMA 通道设置为在硬件请求时触发*/

dmaSetChEnable (DMA_CH0、DMA_HW);

/*启用 TX DMA */

serREG->SETINT =(1 << 16);

}/* scidmaSend */

因此,由于沮丧,我将 scidmaSend()替换为 sciSend(),测试字符串显示正常,并触发 BTCA 中断。 当 BTCAOFFSET 为0时,不调用 dmaGroupANotification()(正如预期的那样)。 所以,要做正确的事情是让 scidmaSend()做正确的事情...

scidmaInit (serREG);/*要求首先调用 sciInit */

/*启用 CPU 中断*/

_enable_IRQ ();

// sci_printf ("scidmaSend 示例-用于将单字节从 RAM 传输到 SCI\n\r\n"DMA);

// scidmaSend (buffer);

sciSend (sciREG1、strlen (buffer)、buffer);

/*在此处输入代码,但不要再次调用 scidmaSend */

/*等待 DMA 中断 ISR 设置标志*/

while (DMA_Comp_Flag!= 0x55AAD09E){

IDLECOUNT++;

}

在 scidmaSend()代码中,有人提到需要针对大端字节序调整地址(而代码现在大概只处理小端字节序)。 在单步执行代码时、我将运行大端字节序。 这会是个问题吗? 或者、它是否仅影响测试字符串的输出、不能正确显示? 我希望 DMA 仍能传输配置的尽可能多的数据字节。 太令人困惑了...

void scidmaSend (char * source_address)

{

#if ((__little_endian__= 1)||(__little_ENDIAN__= 1)

uint8 dest_addr_offset = 0;对于 LE */

其他

uint8 dest_addr_offset = 3;// 3表示为*

#endif

/*等待 DMA 完成任何现有传输*/

while (DMA_Comp_Flag!= 0x55AAD09E);

/*将标志重置为“未完成”*/

DMA_Comp_Flag =~0x55AAD09E;

/*-填充 DMA 控制数据包结构*/

G_dmaCTRLPKT.Sadd =(uint32) source_address;

如果(((serREG->GCR1 >> 10U)& 1U)=0U){/*检查是否为多缓冲模式,请注意 sciREG1不是多缓冲器*/

G_dmaCTRLPKPT.DADD =(uint32)(&(serREG->TD))+dest_addr_offset;//在大型异位设备中,目标地址需要调整*/

G_dmaCTRLPKT.RDSIZE = ACCESS_8_BIT;/*读取大小*

G_dmaCTRLPKT.WRSIZE = ACCESS_8_BIT;/*写入大小*

G_dmaCTRLPKT.FRCNT = strlen (source_address);/*帧计数*

}

否则、如果(serREG = linREG1){

G_dmaCTRLPKT.DADD =(uint32)(&(linREG1->TDx);

/*在大异位设备中,需要调整目标地址

*进行字节访问。 DMA 是一个大端字节序主器件。 但 SCI 发送缓冲器

可通过最低有效字节访问*。 *

G_dmaCTRLPKT.RDSIZE = ACCESS_32_BIT;/*读取大小*

G_dmaCTRLPKT.WRSIZE = ACCESS_32_BIT;/*写入大小*

G_dmaCTRLPKT.FRCNT = strlen (source_address)/4+8;/*帧计数*

}

否则{

返回;//未知寄存器*/

}

我感到困惑。 经过数小时的努力,尝试获取 dmasciSend()以在 sciREG1上发送字符串,没有发生任何事情。 我已经经历了十几次配置、一切似乎都是合理的。 我尝试过各种价值观、但没有成功。 在示例代码中、我看到需要为大端字节序系统以不同的方式设置地址等注释、 但我在《技术参考手册》中看不到任何这方面的内容(鉴于大量的寄存器和选项、在许多具体的详细项目上都很不灵活)。 示例代码中的注释似乎与手册中的文档相冲突。 在基本器件上运行示例代码应该不会那么困难。

我已上传 HL_sys_main.c、该文件应清晰地插入基本的 TMS XL2-570LC43项目中。 此时,将 Update_dma_Comp_Flag()添加到 notification.c 是可选的,因为 DMA 操作似乎根本没有发生。 如果可能、请运行此项目并帮助我调试问题、可能需要 TI 硬件支持。

https://filedropper.com/d/s/HnrWFXoj2ZeQyNpI8nxjBtKbHKbw3R

非常非常感谢。

尊敬的 Peter:

请参阅我的示例:

SCI3将从 SCI1接收数据:

我下载了该文件并将其放入(的副本)上一个 SCI DMA 示例。 编译正常,但它不会在 main()停止。 不知道问题是什么、但它就像这个问题...

这两个项目的 hL_sys_main.c 看起来没有太大不同、因此这是一个模糊的 TI 工具。 我复制了上一个工作示例(源文件夹和工作区)、并且复制运行正常。 因此、放入单个 hL_sys_main.c 文件会导致意外行为。

谢谢。

请尝试此链接...

https://www.dropbox.com/s/307kg2mtzmlekpm/HL_sys_main.c?dl=0

谢谢。

您是否为 TX_DATA 和 RX_DATA 定义了".sharedRAM"段?

附件是我的项目中使用的链接器脚本:

e2e.ti.com/.../2627.HL_5F00_sys_5F00_link.cmd

这解决了 main()上的不停止问题。

如果代码按原样运行、则无法正常运行。sciREG3->FLR (保存在 r 中)停留在0x08000FF4的开头、因此代码会一直等待。 0x4表示 SCI3永远空闲。 我已经将 SCI1和 SCI3设置为9600波特。 如果还有其他与 Halcogen 相关的文件、那么我将需要.hcg 文件。

while ((((r = sciREG3->FLR)& SCI_TX_INT)== 0U)||(((sciREG3->FLR & 0x4)=0x4))

{

R = r;

}/*等待*/

谢谢。

尊敬的 Peter:

谢谢、刚才下载了 hL_sys_main.c

此声明:

G_dmaCTRLPKT.PORTASGN = 4; /*端口 b

应更改为:

G_dmaCTRLPKT1.PORTASGN = PORTA_READ_PORTB_WRITE;

用于发送

或

G_dmaCTRLPKT2.PORTASGN = PORTB_READ_PORTA_WRITE;

接收

在 TMS570LC43x 和 RM57Lx 上、DMA 有两个主端口-与微控制器的总线 矩阵系统连接的 Porta 和 PortB。 DMA Porta 接口为闪存、SRAM 和 EMIF 存储器、PortB 接口为外设寄存器和外设存储器。 发生 DMA 数据读取和写入访问

通过端口 A 或 B

请参阅器件技术参考手册中的"20.1.2系统资源映射"。

对于其它 TMS570LSx 和 RM4x 器件、DMA 只有一 个主端口-端口 B、此端口连接微控制器内存系统。 DMA 数据读取和写入访问 通过端口 B 进行

我进行了以下更改、代码会更进一步。 与 sciSend()消息的情况不同,我在 SCI1上的 Putty 终端上看不到任何使用 scidmaSend()的输出。 但是、我现在确实看到了一个 BTCA 中断、尽管偏移量为0、因此不会向组发出通知。 我不知道是什么导致输出_not _显示。

// g_dmaCTRLPKT.PORTASGN = 4;//端口 b *

G_dmaCTRLPKT.PORTASGN = PORta_read_PORTB_write;/*端口 b *

空 dmaBTCAInterrupt (空)

{

uint32 offset = dmaREG->BTCAOFFSET;

/*用户代码开始(6)*/

/*用户代码结束*/

if (偏移!= 0U)

{

dmaGroupANotification (BTC、偏移- 1U);

}

/*用户代码开始(7)*/

/*用户代码结束*/

}

我认为 DMA 是唯一的"长字"器件、不能容纳连续字节长字器件(如字节寻址中的 RAM)。 因此、需要为小端字节序选择偏移0 mod 4、为大端字节序选择偏移3 mod 4、因为 DMA 从4字节宽总线的该部分中挑选字节数据。 因此、RAM 输入必须每4个字节具有1个字节的数据。 “abcdefgh”将显示为“ae”,后面有任何垃圾。 因此、CPU 必须在发送时适当地设置 RAM 内容、并在接收时适当地挑选数据。 1KB 的实际发送数据需要4KB (或1K 长字)的发送缓冲区。 请确认。

非常感谢。

谢谢你。

"明显"的问题是、缓冲区[]应该位于共享 RAM 中。 我在 hL_sys_link.cmd 中添加了行、并且构建仍然运行。 然后我在 hl_sys_main.c 中添加了有关 buffer[]的 pragma、编译完成、但调试器不再停止在 main ()处。 叹气...

/*编辑 JC 20160102:将这些变量放入写入槽内存中、以便 DMA 和 CPU 的操作得到协调*/

#pragma SET_DATA_SECTION (".sharedRAM")

char buffer[4 * 500];

#pragma SET_DATA_SECTION ()

谢谢。

好的。 修复了最后一个问题。 变量的存储区域必须位于"已初始化数据"部分(以前称为 BSS =基本存储部分)、以便奇偶校验之类的内容不会触发。

#pragma SET_DATA_SECTION (".sharedRAM")

char buffer[4 * 500];

#pragma SET_DATA_SECTION ()

但是、遗憾的是、仍然看不到 SCI1上显示的数据。

谢谢。

非常感谢您上传和分享此项目。 实际上、SCI1确实正确显示了字符串、既是9600波特、也是230400波特。 最重要的是、以可靠、一致、可重现的方式。

我运行此 H_sys_main.c 的项目 仍然未正确显示字符串、但_has_由于某些未知的模糊原因(对我而言)执行了几次。 我只需要它来与您上传的项目保持一致。 这很可能是 Halcogen 的东西。 至少我现在有一个实心参考系进行比较。

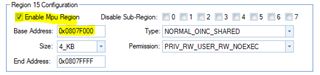

我认为我的问题是由.DIL 文件中的差异引起的、如下所示。 是否有一种"明显"的方法将这些值映射到设置它们的 Halcogen GUI 按钮? 我需要知道它们是什么。 我的.hcg 文件是相同的。

谢谢你。

> DIFF DCDAN_RX.DIL ./DCDAN_RX_new_example/DCDAN_RX.DIL

1c1.

<# TMS570LC4357ZWT 05/21 00:58:13

--

># TMS570LC4357ZWT 06/01/22 04:24:58

133c133

< driver.system.var.core_mpu_region_3_type.value=normal_OIWBWA_nonshared

--

>driver.system.var.core_mpu_region_3_type.value=normal_OIWTNOWA_nonshared

872c872

< driver.system.var.core_mpu_region_3_type_value.value=0x000B

--

> driver.system.var.core_mpu_region_3_type_value.value=0x0002

您能否澄清一下您是手动编辑了.dil 文件、还是 Halcogen 通过一些按钮修改了.dil 文件? 如果是按钮、那么如何在 GUI 中实现它? 我假设 Halcogen 根据我为项目名称提供的 xxx.hcg 名称推断了名称 xxx.DIL。

您将 SRAM 设置更改为 WriteThroughNoWriteAhead、但 core_mpu_region_3_type_value 会发生什么变化?

DIL 工作正常、但我应该了解构建过程。 非常感谢。