大家好、

我的客户对 GPMC 有如下问题。

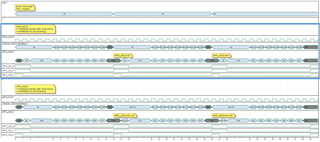

- 在 DMA 包装设置中、当 GPMC 设置为递增(非包装) CSI 时、当16位/16字节猝发写入和128字节写入时、GPMC_AD 输出将会发生什么情况? (以下哪三项?)

- 每个突发写入周期、有效地址变为相同地址

- 每个突发写入周期、有效地址变为+16字节地址

- 以上均不是

- 当 GPMC_WAIT 引脚有效时、CYCLETIME 计数器和 GPMC 设置值之间的关系是什么?

- 当 CYCLETIME 计数器处于冻结状态时、是否准确地说 RDACCESSTIME、WRACCESSTIME、PAGEBURSTACESSTIME 受到影响? 或者、当 CYCLETIME 计数器处于冻结状态时、CSONTIME 和 CSOFFTIME 是否也会受到影响?

此致、

Mari Tsunoda